**SERVICE MANUAL**

olivetti L1

| DATE     | UPDATED PAGES                                                                                                         | PAGES | CODE      |

|----------|-----------------------------------------------------------------------------------------------------------------------|-------|-----------|

| 15-04-83 | 1st Edition of Service Manual. The information was previously contained in the General Service Manual — 3966280 F (1) | 197   | 4100380 V |

| 15-07-83 | vil, viil, 1-16, 1-17, 2-64, 2-67 — 2-73                                                                              | 12    | 4100381 W |

|          |                                                                                                                       |       |           |

|          |                                                                                                                       |       | ,         |

|          |                                                                                                                       |       |           |

|          |                                                                                                                       |       |           |

|          |                                                                                                                       |       |           |

|          |                                                                                                                       |       |           |

|          |                                                                                                                       |       |           |

|          |                                                                                                                       |       |           |

**SERVICE MANUAL**

# olivetti L1

## PUBLICATION ISSUED BY:

Ing. C. Olivetti & C., S.P.A.

Servizio Centrale Documentazione

77, Via Jervis - 10015 IVREA (Italy)

© 1983, by Olivetti

## **PREFACE**

This manual is intended for field engineers.

#### SUMMARY

This manual describes the installation and maintenance procedures, the functional, electrical and mechanical checks, and the diagnostic procedures carried out on the M2O Basic Module.

DISTRIBUTION: Internal(Z)

## **REFERENCES:**

| Product M20       | - Video General Service Manual       | - Code 4100450 U                    |

|-------------------|--------------------------------------|-------------------------------------|

| Product M20       | - Spare Parts Catalogue              | <ul> <li>Code 4100420 Z</li> </ul>  |

| Product M20       | - Schematics                         | <ul> <li>Code 4100430 S</li> </ul>  |

| Product M20       | - Theory of Operation                | <ul> <li>Code 4100400 B</li> </ul>  |

| Product PR1450    | - Service Manual                     | <ul> <li>Code 3963150 V</li> </ul>  |

| Product PR2400    | - General Service Manual             | <ul><li>Code 3955010 Y(1)</li></ul> |

| Product PR1470/90 | - Service Manual                     | – Code 3930470 Z                    |

| Product PR1480    | - Service Manual                     | <ul> <li>Code 3964100 V</li> </ul>  |

| Product PR2300    | - General Service Manual             | - Code 3966450 G                    |

| Product XU4300/1  | - MFDU(320KB) General Service Manual | - Code 3961640 W                    |

| Product XU4302    | - MFDU(640KB) General Service Manual | <ul> <li>Code 3964510 W</li> </ul>  |

| Product XU5005    | - 5.25" HDW Service Manual           | <ul> <li>Code 3964410 V</li> </ul>  |

# L1M20

# SERVICE MANUAL

Publication Code: 4100380 V

Date: April 1983

# Chapter Index

| FUNCTIONAL DESCRIPTION    | 1 |

|---------------------------|---|

| INSTALLATION AND UPGRADES | 2 |

| MAINTENANCE .             | 3 |

| POWER-UP DIAGNOSTICS      | 4 |

| DLITEST                   | 5 |

| SYSTEM TEST               | 6 |

# CONTENTS

| 1-1  | 1. FUNCTIONAL DESCRIPTION           |

|------|-------------------------------------|

| 1-1  | GENERAL                             |

| 1-3  | SYSTEM DESCRIPTION                  |

| 1-5  | DISPLAY                             |

| 1-6  | VIDEO INTERFACE                     |

| 1-6  | MINI-FLOPPY DISK DRIVES             |

| 1-7  | MINI-FLOPPY DISK INTERFACE          |

| 1-7  | MINI-FLOPPY DISK RECORD STRUCTURE   |

| 1-8  | HARD DISK UNIT                      |

| 1-9  | HARD DISK CONTROLLER                |

| 1-9  | KEYBOARD                            |

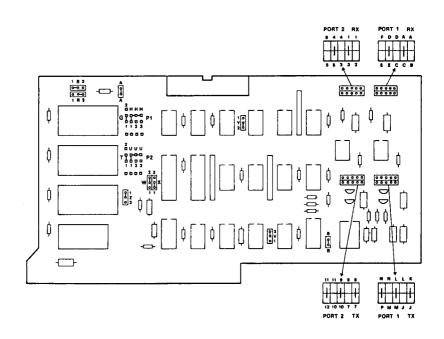

| 1-10 | DUAL COMMUNICATION SERIAL INTERFACE |

| 1-11 | CENTRAL PROCESSOR UNIT (CPU)        |

| 1-11 | MEMORY (RAM and EPROM)              |

| 1-11 | PARALLEL INTERFACE                  |

| 1-12 | TIMER                               |

| 1-12 | OPTIONS                             |

| 1-15 | POWER SUPPLY                        |

| 1-16 | EXTERNAL HARD DISK UNIT             |

| 1-17 | TV ADAPTER                          |

| 2-1  | 2. INSTALLATION AND UPGRADES        |

| 2-1  | INTRODUCTION                        |

| 2-1  | SITE PREPARATION                    |

| 2-2  | INPUT AC ELECTRICAL CHARACTERSITCS  |

| 2-2  | ENVIRONMENTAL REQUIREMENTS          |

| 2-2  | PHYSICAL CHARACTERISTICS            |

PAGE

4100381 W SERVICE MANUAL

- 2-3 CONNECTING THE BLACK & WHITE DISPLAY TO THE BASIC MODULE

- 2-4 CONNECTING COLOUR DISPLAY TO THE BASIC MODULE

- 2-6 CONNECTING A PRINTER TO THE SYSTEM

- 2-16 CONNECTING TO AN AC SOURCE

- 2-16 SWITCHING ON (CPU 1042)

- 2-19 UPGRADES

- 2-19 MEMORY UPGRADE

- 2-22 IEEE 488 INTERFACE

- 2-23 INSTALLATION OF SECOND MINI-FLOPPY DISK DRIVE

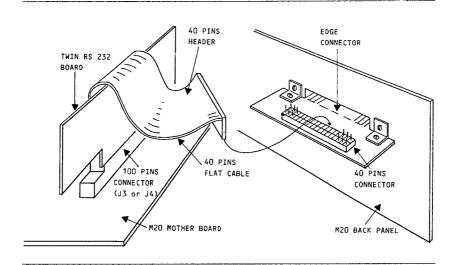

- 2-29 TWIN RS 232C INTERFACE BOARD

- 2-32 INSTALLATION OF APB 1086 BOARD

- 2-34 INSALLATION OF COLOUR DISPLAY

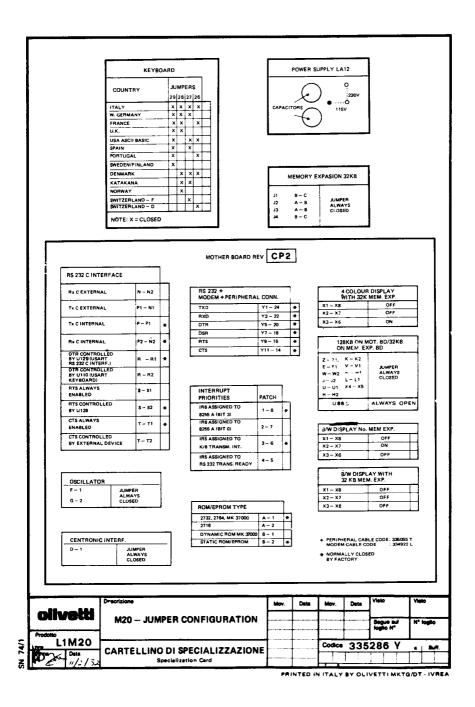

- 2-36 JUMPER CHARTS

- 2-36 KEYBOARD

- 2-37 POWER SUPPLY

- 2-39 32KB MEMORY EXPANSION BOARD

- 2-40 IEEE 488 INTERFACE BOARD

- 2-41 TWIN INTERFACE BOARD

- 2-49 LEVEL COP MOTHERBOARD

- 2-55 LEVEL D MOTHERBOARD

- 2-61 LEVEL D5 MOTHERBOARD

- 2-63 SUMMARY OF JUMPER CHARTS FOR VARIOUS MEMORY CONFIGURATIONS

- 2-64 HARD DISK CONTROLLER JUMPERS

- 2-67 INSTALLATION OF EXTERNAL HARD DISK UNIT

- 2-71 INSTALLATION OF TV ADAPTER

- 3-1 3. MAINTENANCE

- 3-1 INTRODUCTION

viii

- 3-1 SIGNAL ADJUSTMENTS

- 3-1 MOTHERBOARD

- 3-5 POWER SUPPLY

- 3-6 HARD DISK CONTROLLER ADJUSTMENTS

- 3-14 DISASSEMBLY AND ASSEMBLY OF MAIN MODULES

- 3-14 REPLACEMENT OF BASIC MODULE COVER

- 3-16 REPLACEMENT OF KEYBOARD

- 3-17 REPLACEMENT OF MINI-FLOPPY DISK DRIVE(S)

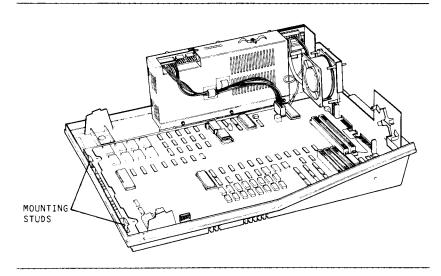

- 3-19 REPLACEMENT OF POWER SUPPLY UNIT

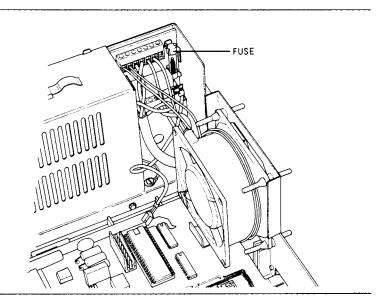

- 3-20 REPLACEMENT OF FUSE

- 3-22 REPLACEMENT OF FAN

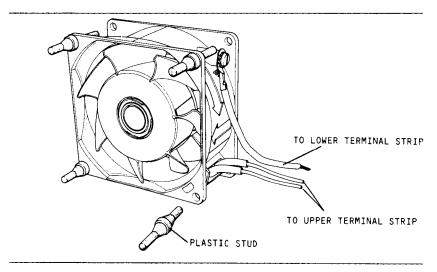

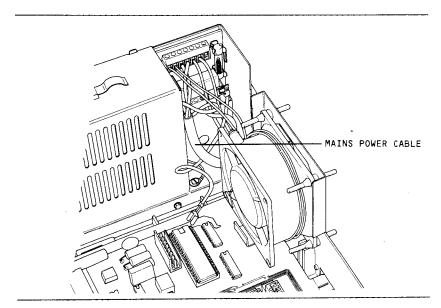

- 3-23 REPLACEMENT OF MAINS POWER CABLE

- 3-24 REPLACEMENT OF MOTHERBOARD

- 3-25 REMOVAL OF KEYMODULE FROM KEYBOARD

- 3-27 REMOVAL OF ON/OFF SWITCH

- 3-28 REMOVAL OF CRT DISPLAY

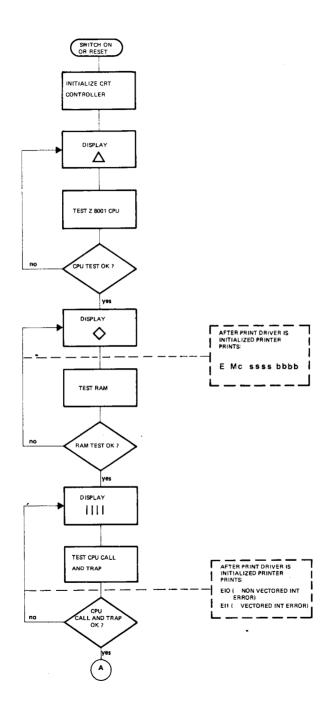

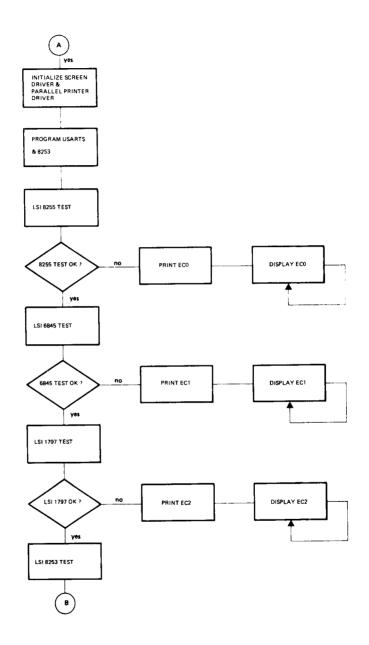

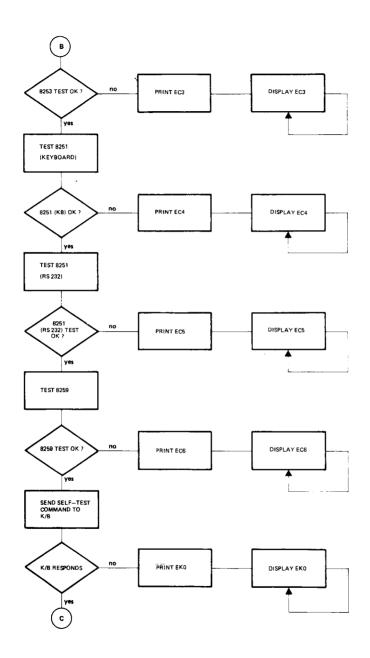

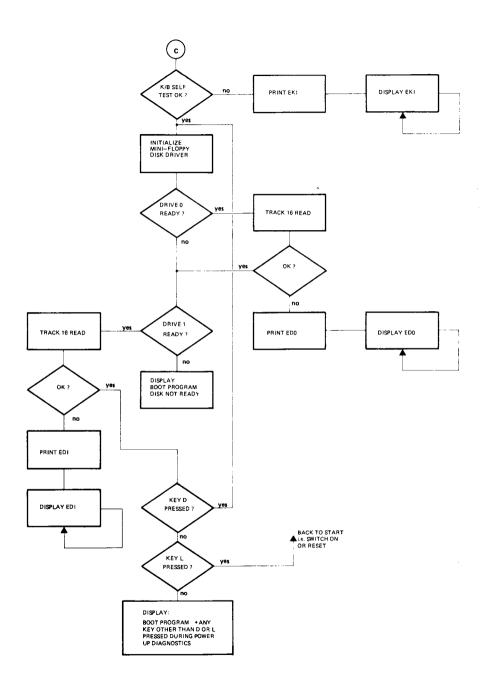

- 4-1 4. POWER-UP DIAGNOSTICS

- 4-1 INTRODUCTION

- 4-1 TEST DESCRIPTION AND OPERATING PROCEDURES

- 4-2 Z8001 CPU TEST

- 4-2 ROM MODULE TEST

- 4-3 RAM MODULE TEST

- 4-3 LSI CHIP TESTS

- 4-3 KEYBOARD TEST

4-4

- 4-3 DISK DRIVE TEST

- 4-5 ERROR MESSAGES AND TABLES AND INTERPRETATION

- 4-6 MESSAGE DISPATCHING

TEST PROGRAM FLOW

# 5-1 5. OLITEST

- 5-1 INTRODUCTION

- 5-1 OPERATING PROCEDURES

- 5-2 VIDEO DISPLAY TEST

- 5-2 KEYBOARD TEST

- 5-3 MOTHERBOARD TEST

- 5-3 MINI-FLOPPY DISK TEST

- 5-3 RS 232C INTERFACE TEST

- 5-3 PARALLEL INTERFACE TEST

- 5-4 IEEE 488 INTERFACE TEST

- 5-4 TEST DESCRIPTIONS

- 5-4 VIDEO TESTS

- 5-5 KEYBOARD TEST

- 5-5 MOTHERBOARD TEST

- 5-6 MINI-FLOPPY D'SK TEST

- 5-7 RS 232C INTERFACE TEST

- 5-7 PARALLEL INTERFACE TEST

- 5-7 IEEE 488 INTERFACE TEST

- 5-8 ERROR MESSAGES

- 5-8 VIDEO ALIGNMENT TEST

- 5-8 KEYBOARD TEST

- 5-8 MOTHERBOARD TEST

- 5-8 MINI-FLOPPY DISK TEST

- 5-8 RS 232C ERROR

- 5-9 PARALLEL INTERFACE ERROR

- 5-9 IEEE 488 INTERFACE TEST

- 5-10 JUMPERS

- 5-10 SERIAL TEST

- 5-13 PARALLEL TEST

- 6-1 6. SYSTEM TEST

- 6-1 INTRODUCTION

- 6-1 OPERATING PROCEDURES

- 6-3 TEST DESCRIPTION

- 6-3 VIDEO MODULE TEST (SELECTED BY DEPRESSING '1')

- 6-3 CPU TEST (selected by depressing '2')

- 6-4 LSI CHIP TEST (SELECTED BY DEPRESSING '3')

- 6-4 KEYBOARD TEST (SELECTED BY DEPRESSING '4')

- 6-6 MEMORY TEST (SELECTED BY DEPRESSING '5')

- 6-7 MINI-FLOPPY FUNCTIONAL TEST (selected by depressing '6')

- 6-9 RS 232C INTERFACE TEST (SELECTED BY DEPRESSING '7')

- 6-9 PARALLEL INTERFACE TEST (SELECTED BY DEPRESSING '8')

- 6-10 PARALLEL PRINTER TEST (SELECTED BY DEPRESSING '9')

- 6-10 MINI-FLOPPY WRITE PROTECT TEST (SELECTED BY DEPRESSING '10')

- 6-10 MINI-FLOPPY ALIGNMENT & ECCENTRICITY TEST

- 6-10 AUTO, TEST (SELECTED BY DEPRESSING '12')

- 6-11 SYSTEM EXERCISOR TEST (SELECTED BY DEPRESSING '13')

- 6-11 OPERATOR ENTERED TEST LIST (SELECTED BY DEPRESSING '14'

- 6-11 CONFIGURE SYSTEM TEST (SELECTED BY DEPRESSING '15')

- 6-11 ERROR MESSAGES

- 6-11 VIDEO MODULE TEST

- 6-11 Z8001 CPU TEST

- 6-12 LSI CHIP TEST

- 6-12 KEYBOARD TEST

- 6-12 RAM MODULE TEST

- 6-14 MINI-FLOPPY DISK TEST

- 6-15 RS 232C INTERFACE TEST

- 6-15 PARALLEL INTERFACE TEST

- 6-15 WRITE PROTECT TEST

- 6-15 FLOPPY DISK ALIGNMENT TEST

- 6-17 SYSTEM EXERCISOR TEST

- 6-17 JUMPERS REQUIRED FOR SYSTEM TEST

- 6-20 SYSTEM TEST FOR HARD DISK

- 6-20 OPERATING PROCEDURES

- 6-21 DRIVE READY TEST (SELECTED BY DEPRESSING '1')

- 6-21 SEEK TEST (SELECTED BY DEPRESSING '2')

- 6-21 DATA PATTERN TEST (SELECTED BY DEPRESSING '3')

- 6-22 RANDOM WRITE. READ AND VERIFY (SELECTED BY DEPRESSING '4')

- 6-23 INSERT TEST (SELECTED BY DEPRESSING '5')

- 6-23 FUNNEL TEST (SELECTED BY DEPRESSING '6')

- 6-23 SCANTION TEST (SELECTED BY DEPRESSING '7')

- 6-23 AGEING TEST (SELECTED BY DEPRESSING '8')

- 6-24 CONTROLLER TEST (SELECRED BY DEPRESSING '9')

- 6-24 FULL EXERCISE (SELECTED BY DEPRESSING 'A')

- 6-24 WRITE/CONTINOUS VERIFY (SELECTED BY DEPRESSING 'B')

- 6-24 FORMAT (SELECTED BY DEPRESSING 'C')

- 6-25 SET PARAMETERS (SELECTED BY DEPRESSING 'D')

- 6-25 HDU DEBUGGING OPTIONS (SELECTED BY DEPRESSING 'E')

- 6-26 SCOPE LOOP SELECTION (SELECTED BY DEPRESSING 'F')

- 6-27 SYSTEM TEST FOR TWIN RS 232C BOARD

- 6-27 OPERATING PROCEDURES

- 6-27 TEST 1 RS 232C DATA INTEGRITY

- 6-28 TEST 2 CURRENT LOOP DATA INTEGRITY

- 6-28 TEST 3 CONTROL LINES

- 6-28 TEST 4 SYNCHRONOUS DATA TRANSFER

- 6-29 TEST 5 BAUD RATE ACCURACY

- 6-29 TEST 6 INTERRUPT SUBSYSTEM

- 6-29 TEST & INTERRUPT DRIVEN DATA TRANSFER

- 6-29 TEST 8 DEFAULT STRING

- 6-30 JUMPER CONFIGURATION

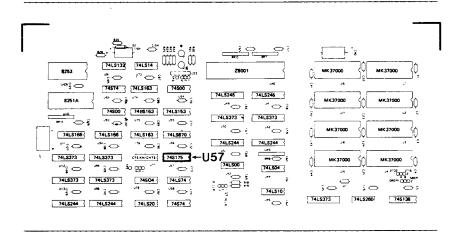

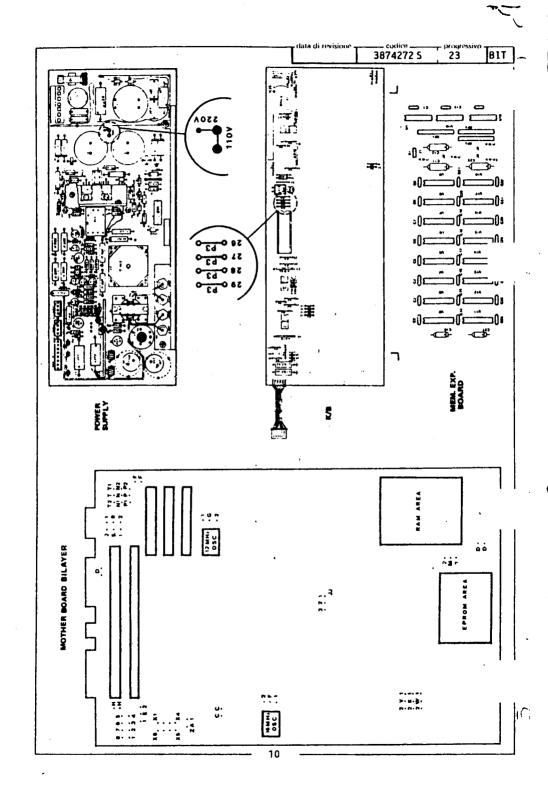

- A-1 A. MOTHERBOARD CIRCUITRY

- B-1 B. LIST OF DATE PUBLICATIONS

- C-1 C. SYSTEM TEST

FUNCTIONAL DESCRIPTION

#### 1. FUNCTIONAL DESCRIPTION

#### 1.1 GENERAL

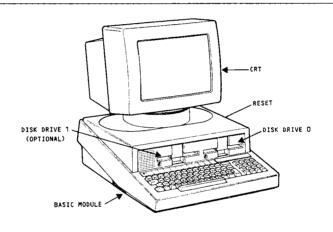

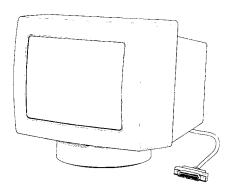

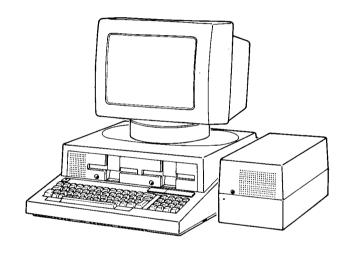

The Olivetti L1 M2O professional computer is a desk top unit and in its standard configuration shown in Figure 1-1 contains two parts:

- CRT Display

-Basic Module

Fig. 1-1 M20 Basic Module & Display

The Display can either be a black and white (B-W) or colour 12 inch CRT. In the case of the colour Display two cables (signal and power) connect the Basic Module to the Display. An intensity control potentiometer is mounted on the back.

The Basic Module houses the motherboard, keyboard, the power supply and one 5.25 inch mini-floppy disk drive. The mini-floppy disk drive provides the ability for using magnetic media for program or data storage. Space is provided for the second optional disk drive which may be a Hard Disk Unit.

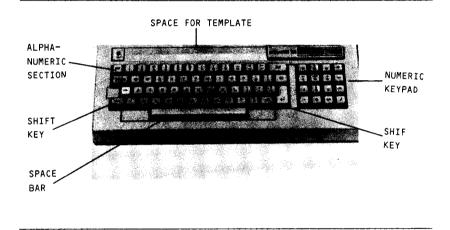

The keyboard provides an alphanumeric character set and a numeric pad. In addition, the keyboard has a power-on lamp and buzzer.

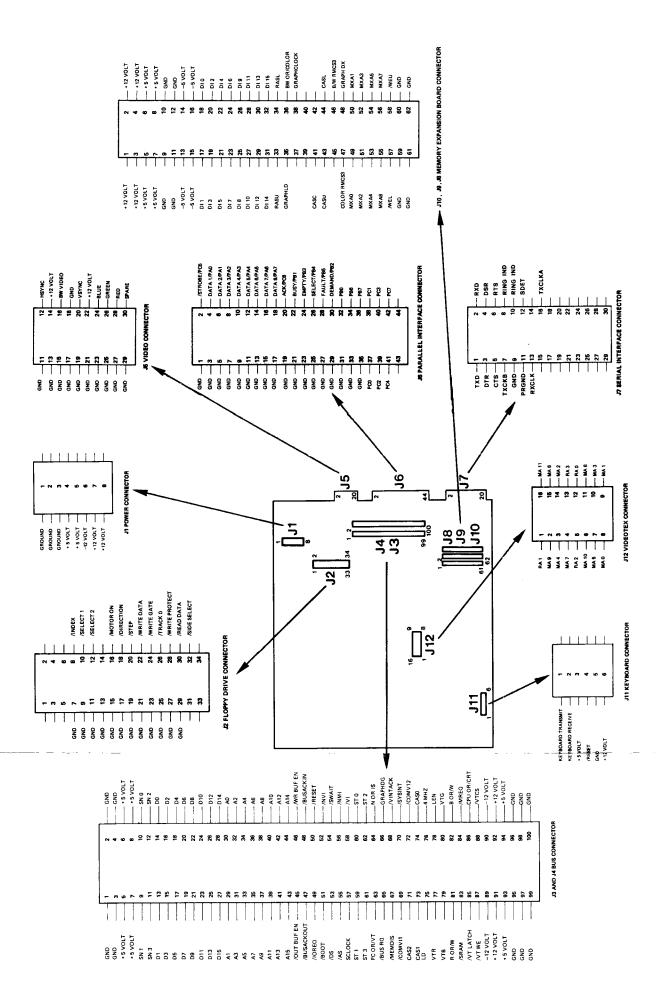

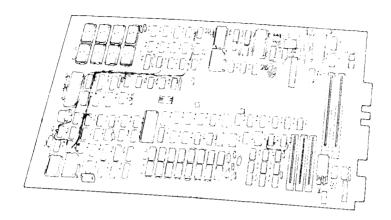

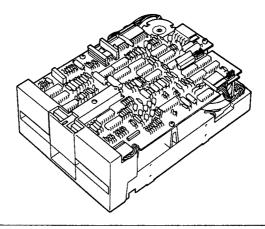

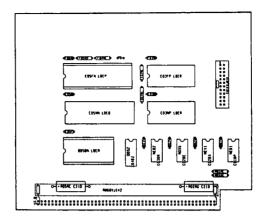

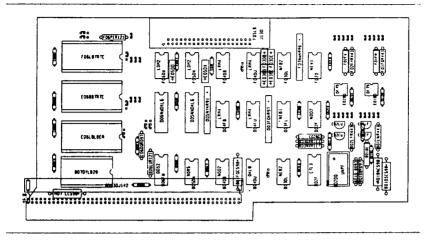

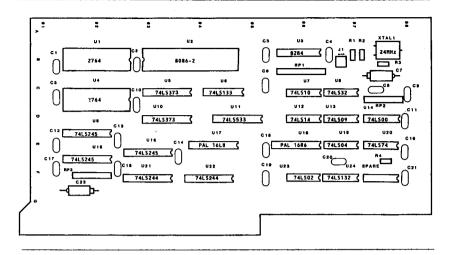

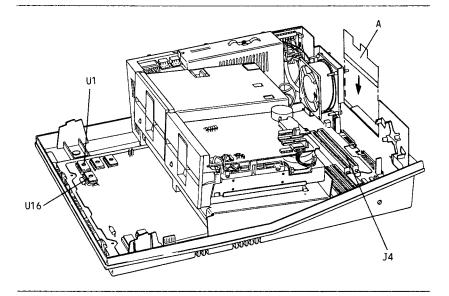

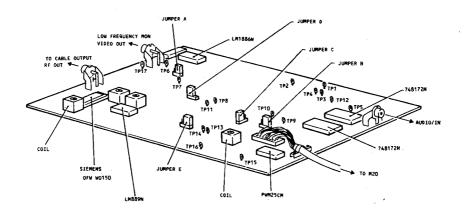

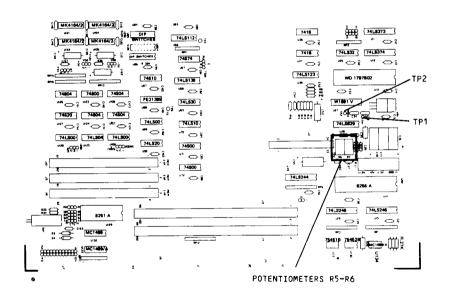

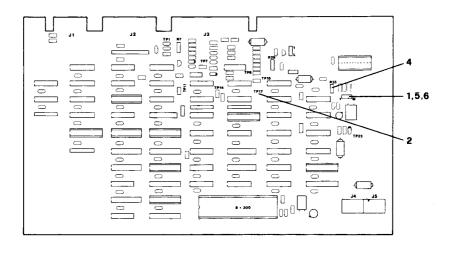

The motherboard is the printed circuit board which takes up most of the bottom of the case and contains the major circuitry for the M20 system.

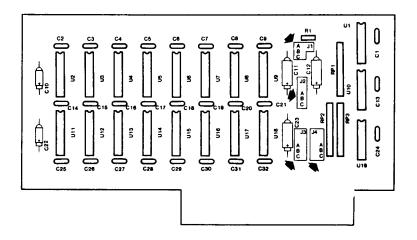

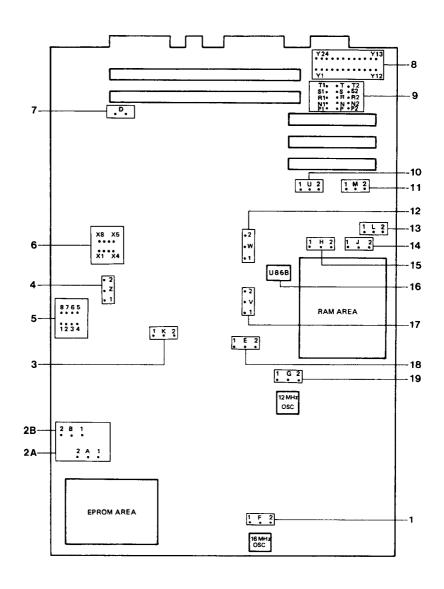

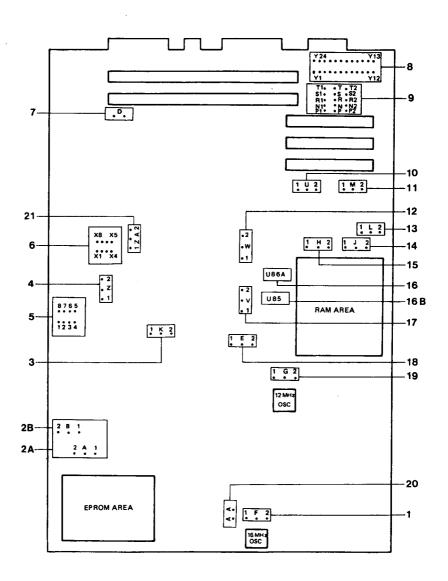

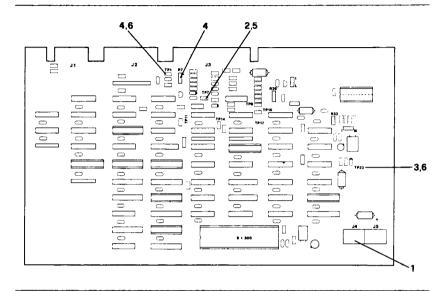

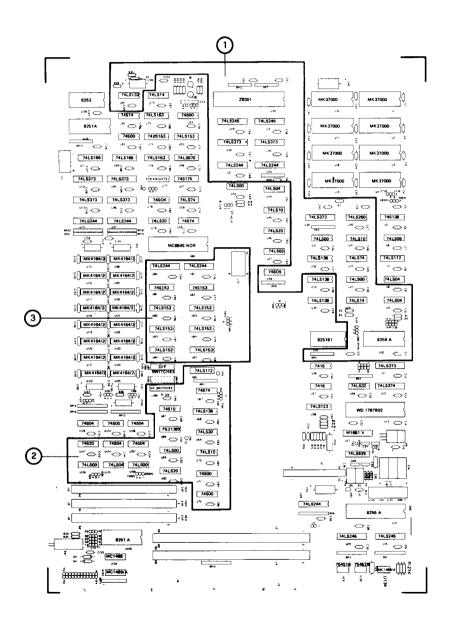

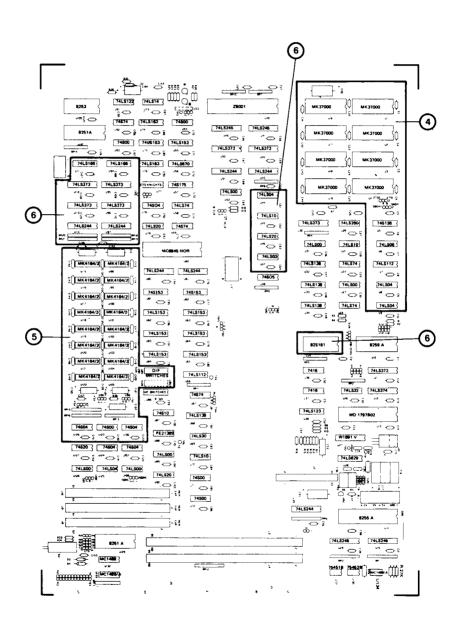

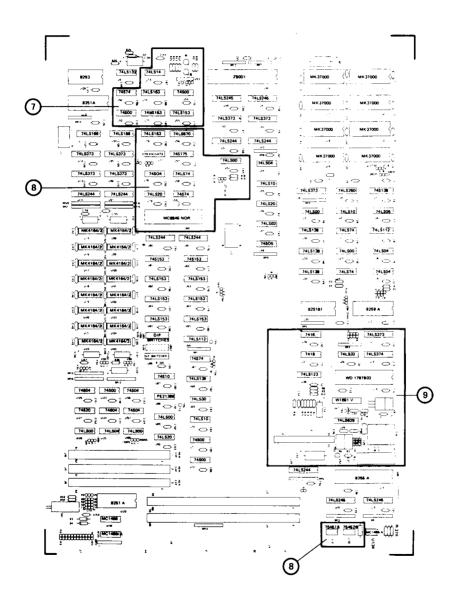

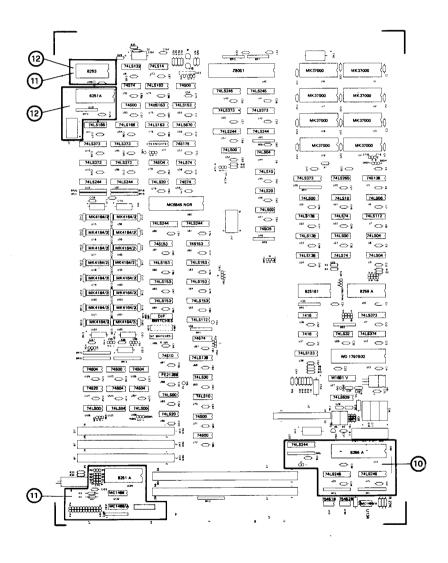

Fig. 1-2 M20 Motherboard

The motherboard holds the microprocessor (CPU), and all of the logic, memory and control circuits for peripheral interfaces (such as interface to printers), and provides space for system expansion.

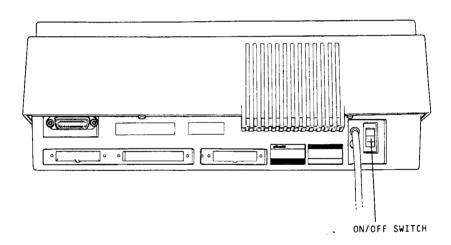

A reset push button is provided to reset the M20 without the use of the power-on switch. This push button is located on the right side of the Basic module, very close to the rear, and does not extend from the cover.

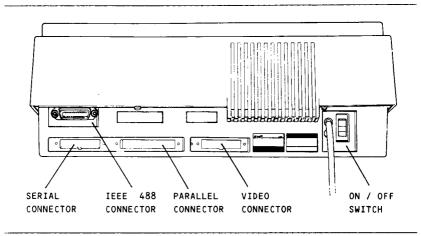

Three cable connectors are provided on the back of the Basic Module for connecting to the Display and other peripheral units. The cable connectors are:

- Video connector

- Parallel Input/Output connector (Centronics-like)

- Serial Input/Output connector (RS 232C)

Space is also provided for connectors for the optional interfaces like the IEEE 488 and the TWIN RS 232C.

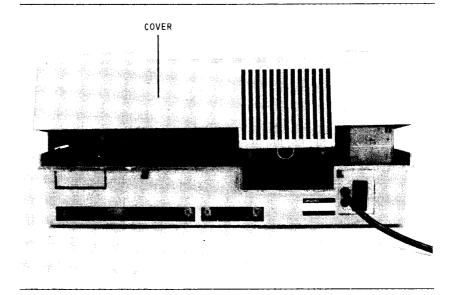

Fig. 1-3 Rear view of M20 Basic Module

#### 1.2 SYSTEM DESCRIPTION

The following summarizes the standard configurations (CPU 1042, CPU 1049), the peripheral options supported, and the expansion options (C).

STANDARD CONFIGURATION - CPU 1042

B-W 12" CRT Display (with graphics capability) Basic Module

72 key keyboard

One 320 Kilobyte (KB) or 160KB or 640KB mini-floppy

disk drive

Motherboard

Z8001 Microprocessor

128 KB Random Access Memory

8 KB Erasable Programmable Read Only Memory

Parallel Input/Output Interface (Centronics-like)

Dual Communication Serial Interface (RS 232C)

STANDARD CONFIGURATION - CPU 1049

B-W 12" CRT Display (with graphics capability)

Basic Module

72 key keyboard

1 Hard Disk unit

#### EXPANSION OPTIONS - C

Colour CRT Display

Three 32 KB RAM Memory Expansion Boards (System Memory = 224 KB)

or

Three 128 KB RAM Memory Expansion Boards (System memory = 512 KB)

Second Mini-Floppy Disk Drive (for systems with CPU 1042)

Parallel Printers

80 or 132 column matrix printer

Peripheral expansion Boards

IEEE 488 Interface Board

TWIN RS 232C Interface Board

Alternate Processor Board (APB) 1086(only with CPU 1042)

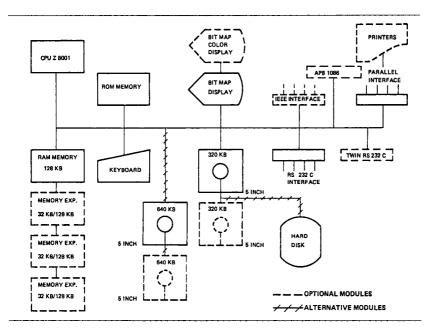

A simple block diagram of the M20 is shown in figure 1-4. The dotted lines show the optional features. A brief explanation of each module shown in figure 1-4 follows.

Fig. 1-4 M20 Simple Block Diagram

#### 1.2.1 DISPLAY

In its minimum configuration the system uses a black and white Display, and a bit-mapped approach for both graphics and text. The resolution is 512 by 256 dots. The character set includes upper-case and lower-case. Standard display attributes include reverse and hide capabilities. Attributes are all software defined. Figure 1-5 shows the black and white Display.

Fig. 1-5 Black & White Display

The use of the bit-map technique permits the possibility of obtaining two different video page formats (1024/2000 characters) on the same system. These formats can be selected by means of parameters. The choice of either a 1024 or 2000 character page takes place at the moment of the system start up by means of specific parameters handled by the operating system. There is no hardware difference between the two formats. The two formats have the following characteristics:

1024 characters

characters per line: 64

number of lines: 16

net character matrix: 5 x 7

gross character matrix: 8 x 16

2000 Characters

Characters per line: 80 number of lines: 25 net character matrix: 5 x 7 gross character matrix: 6 x 10

A colour display is available as a standard option. There are two different types of colour systems:

- 4 colour

- 8 colour

In the 4 colour system eight colours are available but only four may be viewed simultaneously. In the eight colour system all the eight colours may be viewed simultaneously. The Display unit used for both systems is the same. The eight colour palette is composed of red, green, yellow, blue, magenta, cyan, black and white.

Resolution in colour is the same as in Black and White for the bit-mapped graphics but the memory requirements is higher for the colour systems. The 4 colour system requires 32 KB of RAM, the 8 colour one requires 64 KB of RAM while the Black and White only requires 16 KB of RAM.

#### 1.2.2 VIDEO INTERFACE

The video interface provides the interface between the Display and the M2O system as well as the hardware associated with the generation of graphics and text. It is physically found on the motherboard.

#### 1.2.3 MINI-FLOPPY DISK DRIVES

One 5.25 inch Mini-Floppy Disk Drive must always be present on an M20 system. There are three types of mini-floppy disk drives:

- 160 KB (unformatted capacity) Mini-Floppy Disk drives

- 320 KB (unformatted capacity) Mini-Floppy Disk drives

- 640 KB (unformatted capacity) Mini-Floppy Disk drives

If two mini-floppy disk drives are used, they must be of the same type. Only 320 KB or the 640 KB mini-floppy disk drives can be used as a Hard Disk back up device.

4100380 V

1-6

Fig. 1-6 320 KB Mini-Floppy Disk Drive

#### 1.2.4 MINI-FLOPPY DISK INTERFACE

The  $\min$ -floppy disk interface provides two major functions for the M20 system:

- It controls the logic and control circuitry needed to control and record data onto, or to read data from the 5.25 inch mini-floppy disks - It initially formats new disks

The mini-floppy disk interface is physically located on the motherboard.

#### 1.2.5 MINI-FLOPPY DISK RECORD STRUCTURE

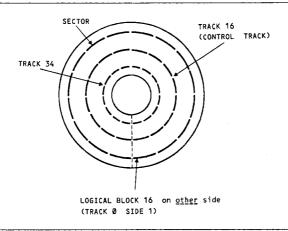

This section provides background information on the mini-floppy disk formats (320KB). A mini- floppy consists of a plastic disk, coated with magnetic media suitable for recording or storing information. Information is recorded as a series of magnetic flux reversals, on the surface of the disk. The structure is somewhat similar to a phonograph record. There are a number of seperate concentric circles, called tracks holding the data. There are two moving parts: the disk which rotates continously, and the Read/Write head which must be positioned over the selected track.

Each track is broken up into short sections called SECTORS. Each sector in double-density mode, can store 256, 512 or 1024 bytes of data. The M2O 32O KB Mini-Floppy Disk drive chooses the 256 per sector drive. A byte is 8 bits long and in general can be thought of as a stream of 8 bits. On the 32O KB Mini-Floppy Disk drive there are 35 concentric tracks. Since there are 35 x 16 sectors in all, the maximum data

recording capacity is 560 x 256 bytes or 143.36 KB on each recording side. The total recording capacity is actually more than this, since each sector also contains data for identifying tracks and sectors, and redundancy marks for making error checks. Without the track and sector identification, data could not be recovered. Without redundancy checks, it would not be known whether errors had occurred. Track and sector information are recorded on the disk when it is formatted. In addition, one or more tracks are reserved for a directory which enables the Operating System (OS) to keep track of the files. Because the user's file may be longer than 256 bytes, a file may consist of a string of sectors, but not necessarily in sequential sectors. Directory information is "data" and is recovered in the DATA section of a sector. One or more tracks are reserved for the directory, and listing of the location of the files. Each time the OS adds or deletes a file, it also updates the directory.

Fig. 1-7 320KB Disk Structure

#### 1.2.6 HARD DISK UNIT

The M20 can use a 5.25 inch Winchester type Hard Disk Unit. The Hard Disk Unit is housed in the M20 Basic Module and is of the same size as the mini-floppy disk drive. The Hard Disk Unit has a storage capacity of 11.25 Mbytes (unformatted). It has three fixed platters and six read/write heads. It has 33 sectors per track, 1080 tracks and 180

Fig. 1-8 Hard Disk Unit

#### 1.2.7 HARD DISK CONTROLLER

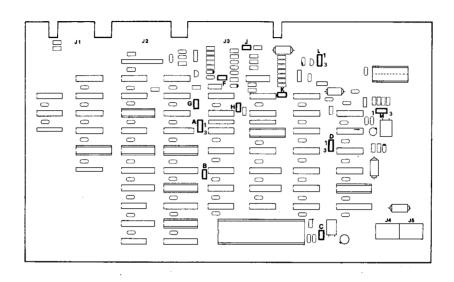

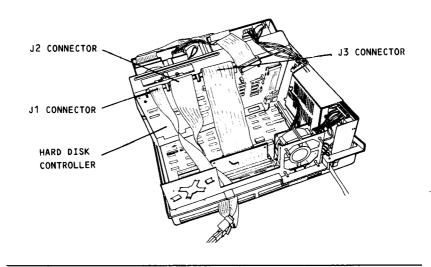

The Hard Disk Controller interfaces the M2O to the Hard Disk Unit. It ensures proper operation of the Hard Disk Unit and error handling. It receives commands from the M2O, decodes them, and then initializes and monitors the hardware as the command is executed and return the status back to the M2O. The Hard Disk controller is physically located on two printed circuit boards:

- a board which is located under the Hard Disk Unit itself

- a small board which plugs into one of the expansion slots on the motherboard.

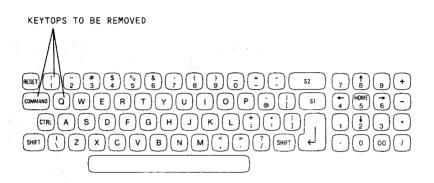

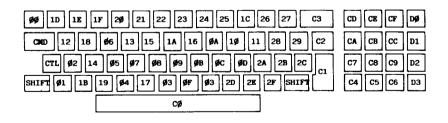

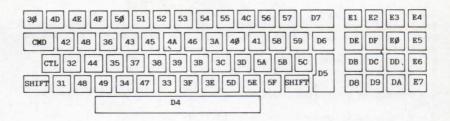

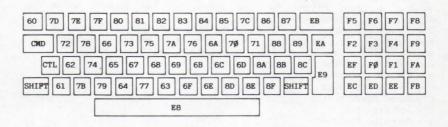

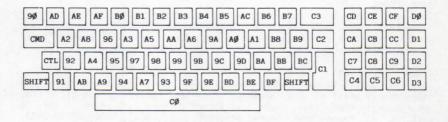

#### 1.2.8 KEYBOARD-

The keyboard has 72 keys. These have been divided into two zones:

- Alphanumeric

- Numeric

There are 4 shift keys. Two grey ones (known as SHIFT) are used for the selection of upper case/lower case. There is a BLUE SHIFT (CONTROL) key which is used in combination with other characters for a variety of operations, mostly in BASIC. There is also a YELLOW SHIFT (COMMAND) which is used together with the "?/" key to provide a shift lock for the letters A-Z.

The M20 can support the following national keyboards:

Italian (0)

USA ASCII (4)

French (2)

British (3)

German (1)

Spanish (5)

Portuguese (6)

Danish (8)

Swedish and Finnish (7)

Norwegian (11)

Swiss - French (13)

Swiss - German (14)

Katakana (9)

Greek (12)

Jugoslavian (10)

The national keyboards are all jumper selectable (except for Greece and Jugoslavia and can be invoked by the PCOS command Set Language (SL). The numbers in parenthesis are the country codes used in the SL command. for example the command "SL 8" sets the Danish keyboard.

Fig. 1-9 USA ASCII Keyboard

#### 1.2.9 DUAL COMMUNICATION SERIAL INTERFACE

The DUAL Communication Serial Interface found on the motherboard provides the M20 with one RS 232C type serial interface and one keyboard interface. The serial RS 232C interface is used to interface the M20 to a modem or plotter.

The keyboard interface provides the interface between the M2O system and keyboard.

#### 1.2.10 CENTRAL PROCESSOR UNIT (CPU)

The M20 uses an advanced 16 bit microprocessor, the Z8001. Some of the features of the Z8001 are:

- sixteen 16 bit general registers

- segmented addressing

- hanling of bit, byte, word and long word data

- three types of interrupts: non-maskable, non-vectored, and vectored. The support logic provides address translation for optimum flexibility in both hardware configuration and software utilization.

#### 1.2.11 MEMORY (RAM and EPROM)

In the standard configuration the M2O holds 128 KB of Random Access Memory (128KB.are located on the motherboard itself) and 8 KB of Erasable Programmable Read Only Memory (EPROM), also physically located on the motherboard itself.

All RAMs are dynamic and require periodic refresh. The bit-mapped black and white CRT requires 16KB of refresh RAM; the 4 colour Display requires 32 KB of refresh RAM; the 8 colour Display requires 64 KB of refresh RAM. The Basic Interpreter and Operating System (loaded from mini-floppy disk) require approximately 64 KB of RAM (loaded from mini-floppy disk). In the standard configuration usually 48 KB are available for programming use. Of this, at least 37 KB are available for user programs. The RAM memory is expandable to 224 KB by inserting three plug-in boards of 32 KB each. The RAM memory can also be expanded to 512 KB if three plug-in boards of 128 KB each are inserted instead of the 32 KB ones.

The 8 colour Display requires either two 32KB memory expansion boards or two 128KB memory expansion boards. The 4 colour display requires one 32KB memory expansion board.

The 8 KB of EPROM on motherboard contain:

- Power On Bootstrap

- Power On Diagnostics

Information in EPROM is placed there in the process of manufacturing the EPROMs. Information stored in the EPROMs as opposed to that stored in RAMs does not appear when thr power is turned off.

#### 1.2.12 PARALLEL INTERFACE

The Parallel interface provides the M20 with one Centronics-like parallel port for connecting a printer. A printer may be one of the following:

Printer PR 2400

Printer PR 1450

Printer Pr 1471

Printer PR 1481

Printer 2300

#### 1.2.13 TIMER

The timer is a programmable device that has three independent channels. Two of the channels are used to set the keyboard and printer baud rates. The third channel is available to the user and can be programmed as an interval real-time clock.

#### 1.2.14 OPTIONS

The options on the M20 are:

- IEEE 488 Interface Board

- TWIN RS 232C Interface Board

- Alternate Processor Board (APB) 1086

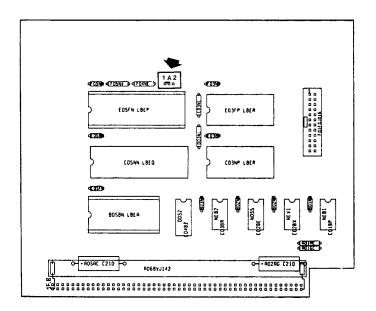

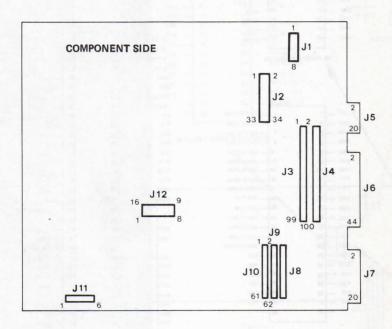

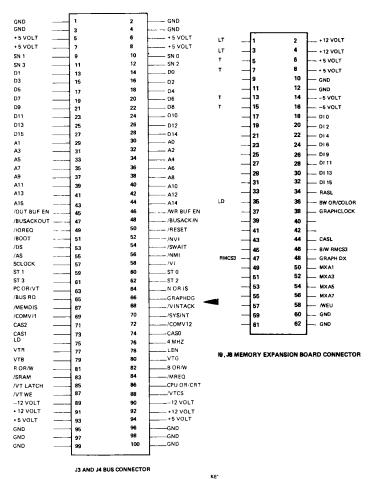

All of the above options may be plugged into slots  ${\tt J3}$  or  ${\tt J4}$  on the  ${\tt motherboard}.$

#### 1.2.14.1 IEEE 488

The IEEE (Institute of electrical and Electronic Engineers) 488 board provides a means to transfer digital data among a group of instruments and system components. As implemented in the M2O, the IEEE option consists of a plug-in miniboard containing six integrated circuits providing TALKER, LISTENER and CONTROLLER functions plus line transceivers. It can be used with systems that use a byte-serial means of data transfer. These interface functions are described below.

LISTENER - A device capable of receiving data over the interface when addressed. Examples of this type of device are printers, display devices, programmable power supplies, programmable signal sources and the like

TALKER - A device capable of transmitting data over the interface when addressed. Examples of this type of device are tape readers, voltmeters that are outputting data, counters that are outputting data and so on.

CONTROLLER - A device capable of specifying talkers and listeners for data transfer. Examples of this are computers like the M20.

1–12 4100380 V

Fig. 1-10 IEEE 488 Board

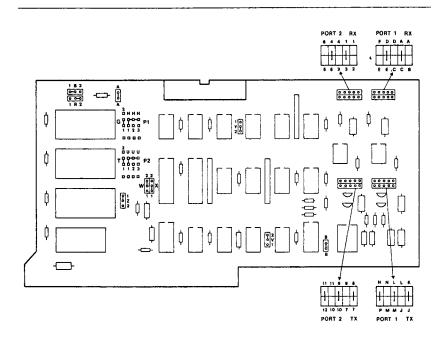

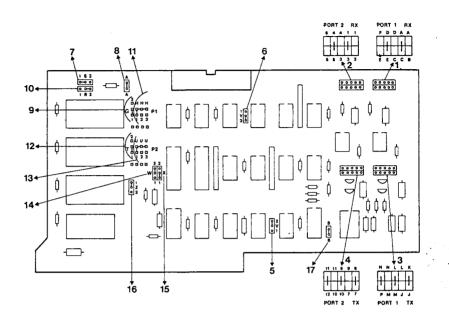

#### 1.2.14.2 Twin RS 232C Interface Board

This interface board provides two communication channels with both RS 232C and 20mA current loop option. It supports asynchronous and synchronous communication and various BAUD rates are easily programmable for each channel. The use of an intelligent interrupt controller enables a real type of software capabilities. The board is provided with capabilities of both receiving and transmitting the transmit and receive data clocks for the synchronous communications. The board can be configured as follows:

- 2 RS 232C Channels

- 2 Current Loop Channels

- 1 RS 232C Channel and 1 Current Loop Channel

Fig. 1-11 Twin RS 232C Board

#### 1.2.14.3 Alternate Processor Board 1086

The Alternate Processor Board (APB) 1086 is a plug in board which allows the M20 to execute software written for an Intel 8086 microprocessor. The purpose of this board is to support the following two widely used operating systems: CP/M 86 MS-DOS

Fig. 1-12 APB 1086 Board

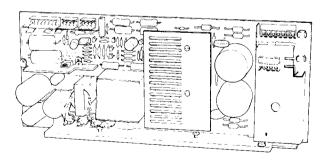

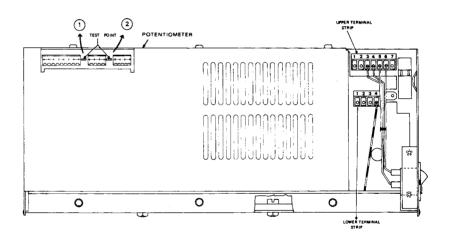

#### 1.2.15 POWER SUPPLY

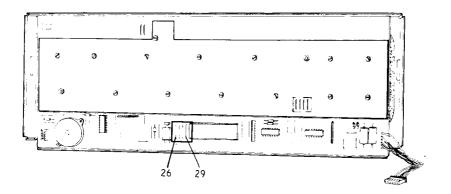

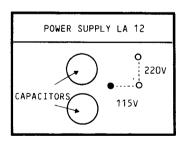

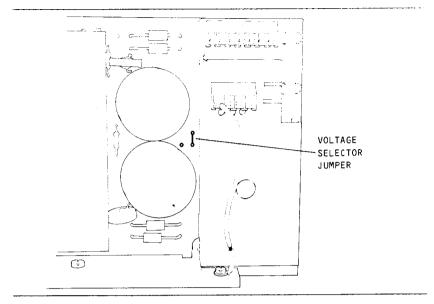

The M2O power supply is housed in a metal case inside the Basic Module. It provides the correct power source to all L1 M2O circuitry. It is a switching type of power supply. A voltage selector jumper is present in the power supply. This jumper selects one of the following AC line input voltages:

100 - 120 Volts A.C.

200 - 240 Volts A.C.

Fig. 1-13 M20 Power Supply

#### 1.2.16 EXTERNAL HARD DISK UNIT

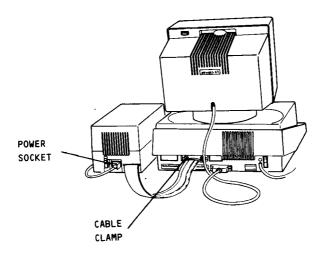

The external hard disk unit is an optional feature which can be added to an M20 with a configuration of 2 minifloppy disk drives. It resides in a seperate case placed beside the M20. The H.D.U. module include:

- the XU 5005 5.25" Hard Disk Unit

- a power supply unit which provides power to the HDU

- a smal<sup>®</sup> interface board IF162

Fig. 1-13 The M20 with the External Hard Disk Unit Module

The aim of the external H.D.U is to increase the disk capacity of the M20 by another 11.25 Mbytes (unformatted).

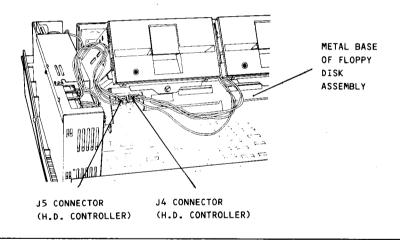

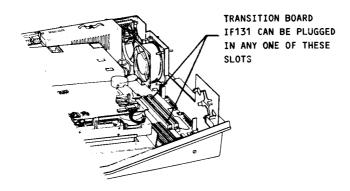

The external H.D.U. is connected to the M20 via the Hard Disk Controller G0223 which resides at the bottom of the floppy disks assembly and via the transition board which plugs into the connectors J3 or J4 of the motherboard. These two boards are the same boards used to interface the internal hard disk unit to the M20 although two modifications have to be made on each board.

The H.D.U. module has its own power supply unit and does not use the M2O's power supply.

Also an LED on the front of the H.D.U. module is present to indicate that the disk unit is selected.

The function of the interface board IF162 is to inhibit any data to be written on the disk drive while the M20 is being switched on or off.

The software and diagnostic procedures relative to the integrated hard disk unit are still valid for the external hard disk unit.

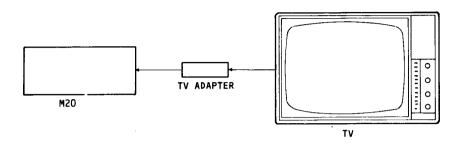

# 1.2.17 TV ADAPTER

The TV adapter is a device which permits the connection of one or more TV sets to the M20. It can be used with the PAL system (in Europe) as well, as with the NTSC system (in USA).

Its principal characteristics are as follows:

# NTSC VERSION

1. Video resolution 256 dots x 200 lines

42 characters x 19 lines

2. TV signal NTSC format

3. TV set 525 cycle/60 Hertz

PAL VERSION

1. Video resolution 256 dots x 232 lines

42 characters x 25 lines

PAL format 2. TV signal

3. TV set 625 cycle/50 Hertz

The minimum number of colours that can be visualised at a time is 4 while the maximum number is 16. The choice is done from a palette of 512 colours.

INSTALLATION AND UPGRADES

| , |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

# 2. INSTALLATION AND UPGRADES

# 2.1 INTRODUCTION

This chapter deals with the site preparation, environmental requirements, installation procedures, printer jumper charts, upgrades, jumper charts for the various boards and motherboard, and connector descriptions.

# 2.2 SITE PREPARATION

The M2O operates reliably in a typical office environment but it is important to adhere to the following points when choosing a suitable site:

- 1) THE M20 SHOULD BE PLUGGED INTO AN EARTHED POWER SUPPLY. Unearthed machines do not work properly and can be a safety hazard. If the M20 is not plugged into an earthed circuit one can experience:

- improper program operation

- unreadable disks

- expensive machine damage

The M2O should when possible be isolated from sources of electrical noise, and from devices that can cause excessive voltage level variations. Some common sources of electrical noise are:

- air conditioners, fans and large blowers

- transformers and alternators

- large brush type or induction motors such as those used on elevators

- ${\operatorname{\mathsf{-}}}$  radio and TV transmitters, signal generators and high frequency security devices

Note: Some of the normal small office machines (typewriters, small copiers, calculators etc) are allowed on the same line provided that they do not cause excessive interference on the line.

- 2) The M2O should be placed in a relatively dust-free place. Airborne dust, dirt and smoke can cause excess wear on moving surfaces, short and open circuits (especially in the presence of high humidity) and read/write errors on the disk.

- 3) The M2O should be placed away from heat and direct sunlight. Unusually high temperatures coupled with low humidity can cause static problems.

- 4) The M2O is cooled by a fan at the rear. This area must be kept clear of papers or other materials that would obstruct air flow.

# 2.3 INPUT AC ELECTRICAL CHARACTERISTICS

The M20 input electrical characteristics are listed below.

- 1) Monophase, alternating voltage with the following nominal voltages: 100 to 120 Volts or 200 to 240 Volts. The voltage ranges are jumper selectable in the power supply itself.

- 2) Permanent driftings of input voltage: +10%, -10% Consequently the two ranges of operation are: 90 Volts to 132 Volts; 180 to 264 Volts.

- 3) Nominal frequency : 50Hz or 60Hz with the same model without any variation.

- 5) Frequency driftings +5%, -5%

# 2.4 OUTPUT DC ELECTRICAL CHARACTERISTICS

| VOLTAGE    | TOLERANCE | CONTINOUS CURRENT | MAX RESIDUAL<br>RIPPLE |

|------------|-----------|-------------------|------------------------|

| + 5 Volts  | 5%        | 3.3/8.9 Amperes   | 50mVp-p                |

| + 12 Volts | 3%        | 2.0/6.2 Amperes   | 100mVp-p               |

| - 12 Volts | 5%        | .03/.7 Amperes    | 100mVp-p               |

# 2.5 ENVIRONMENTAL REQUIREMENTS

Operating Environment:

temperature: 10 degrees to 40 degrees Centigrade (50 to 104 F)

relative humidity: 10% to 95%

Nonoperating Environment

temperature: 5 dgrees to 45 degrees Centigrade (41 to 113 F)

relative humidity: 5% to 95%

Heat Dissipation: 140 watts (477.7 BTU/hour)

# 2.6 PHYSICAL CHARACTERISTICS

WEIGHT

Basic Module:

with one mini-floppy disk drive 9.2Kg (20.24lbs) with two mini-floppy disk drives 11Kg (24.2lbs)

with one mini-floppy disk drive and Hard Disk 11.6Kg (25.6lbs)

Display: 9 Kg (19.8lbs)

## PHYSICAL DIMENSIONS

Basic Module:

Width: 43cm (17.2in); height: 15.5cm (6.2in); depth: 51.9cm (20in)

Display:

Width: 33.4cm (13.36in); hight: 26cm (10.4in); depth 31cm (12.4in)

# 2.7 INSTALLATION

This section describes how the M2O computer system should be installed. To ensure a smooth, easy set-up one has to adhere to the following instructions carefully.

# 2.7.1 CONNECTING THE BLACK & WHITE DISPLAY TO THE BASIC MODULE

The Black and white Display is connected to the Basic Module by means of a single cable. One end of this cable is already fastened to the display. The other end has a connector with two screws at the edges. This connector fits into the edge connector at the rear of the Basic Module as shown in figure 2-1. This edge connector on the motherboard is J5.

Fig. 2-1 Installing the B/W Display

The connector at the end of the cable is referred to as P5. The

connector P5 cannot be fitted the wrong way as a plastic key inside the connector prevents this. The two screws at the edge of P5 are then tightened so as to firmly seat P5 into position.

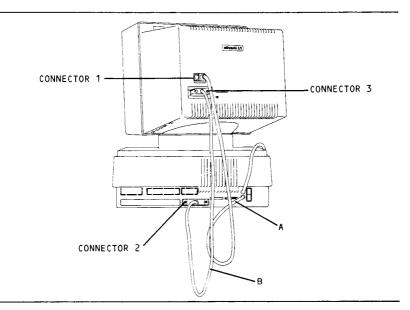

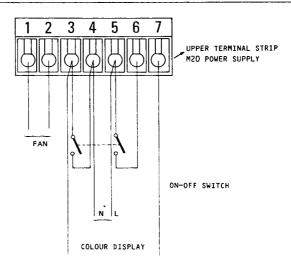

### 2.7.2 CONNECTING COLOUR DISPLAY TO THE BASIC MODULE

The colour Display is connected to the Basic Module by means og two cables:

- Power Cable (A)

- Signal Cable (B)

See figure 2-2 below.

Fig. 2-2 Installing the Colour Display

One end of the power cable A is already fastened to the Basic Module and exits from the bottom hole to the left of the ON/OFF switch at the rear of the Basic Module. The other end of this cable plugs into the top connector (connector 1) at the back of the Colour Display. One end of the signal cable (connector 2) has a connector with two screws at the edges. This connector 2 fits into the edge connector at the rear of the Basic Module. This connector cannot be fitted the wrong way round as a plastic key inside the connector 2 prevents this. The two screws at the edge of connector 2 are then tightened with a screwdriver so as to firmly seat the connector in position.

The other end of this signal cable has a connector (connector 3) which fits at the back of the Display. This slot has two locking springs to clamp connector 3 firmly in position.

NOTE: For 4 colour systems 1 colour memory expansion board must be plugged into the M2O motherboard. For 8 colour systems, 2 colour memory expansion boards must be plugged into the M2O motherboard. See the table below.

| CONFIGURATION                                             | 21-2-22 | K1-K-K2 | E1-E-E2 | v1-v-v2 | w1-w-w2 | #1 <b>-</b> #-#2 | x1 - x8 | x2 - x7 | x3 - x6 | U62/3/4/5          | U86 A |

|-----------------------------------------------------------|---------|---------|---------|---------|---------|------------------|---------|---------|---------|--------------------|-------|

| M 20 WITH OUT<br>ANY EXPANSION<br>BOARDS                  | z - z1  | K - K2  | E - E1  | v - v1  | w - w2  | M - M1           | OFF     | ON      | OFF     | ICs PRESENT        | 011   |

| M 20 WITH AT<br>LEAST ONE B/W<br>32KB EXPANSION<br>BOARD  | z - z1  | K - K 2 | E - E1  | v - v1  | n - A5  | M - N1           | OFF     | OFF     | OFF     | ICs PRESENT        | 01 f  |

| M 20 WITH AT<br>LEAST ONE B/W<br>128KB EXPANSION<br>BOARD | 2 - 21  | K - K1  | E - E1  | v - v2  | w - w1  | M ~ M2           | ON      | OFF     | OFF     | ICS NOT<br>PRESENT | ON    |

| M 20 WITH ONE<br>32KB COLOUR<br>BOARD<br>(4 COLOURS)      | z - z1  | K - K2  | E - E1  | v - v1  | M - MS  | м - м1           | OFF     | OFF     | ON      | ICs PRESENT        | ÇFF   |

| M 20 WITH ONE<br>128KB COLOUR<br>BOARD<br>(4 COLOURS)     | 2 - 21  | к - к1  | E - E1  | v - v2  | W - W1  | M - M2           | OFF     | ON      | ON      | ICS NOT<br>PRESENT | ON    |

| M 20 WITH TWO<br>32KB COLOUR<br>BOARDS<br>(8 COLOURS)     | z - 21  | K - K2  | E - E2  | v - v1  | W - W2  | H - H1           | ON      | OFF     | ON      | ICS PRESENT        | OFF   |

| M 20 WITH TWO<br>128KB COLOUR<br>BOARDS<br>(8 COLOURS)    | z - 21  | K - K1  | E - E2  | v - v2  | w - w1  | M - M2           | ON      | ON      | ON      | ICS NOT<br>PRESENT | ON    |

# 2.7.3 CONNECTING A PRINTER TO THE SYSTEM

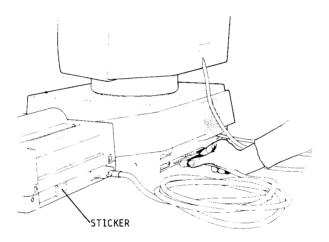

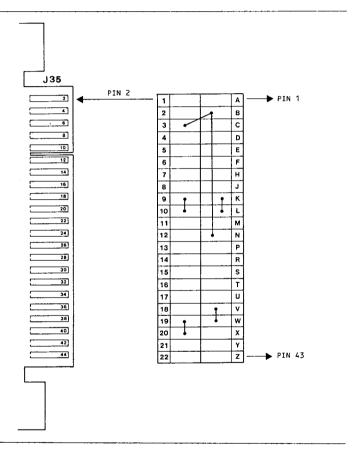

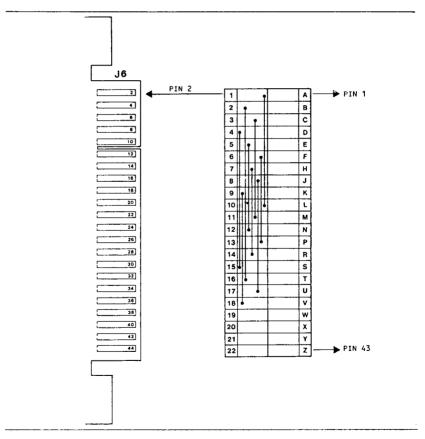

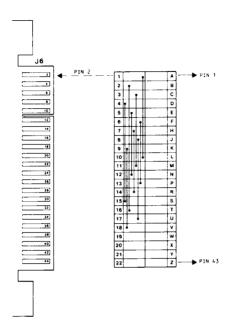

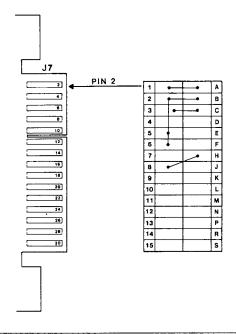

Parallel printers are connected to the M20 via the Centronics-like parallel interface. The jumper charts for the five types of printers are given in sections 2.6.3.1 to 2.6.3.7. The cable used for such a connection is the same for all printers. The connector on one end of the cable plugs into the edge connector of M20 J6. This connector on the end of the cable has two screws at the edges. The other connector at the other end of the cable fits into the connector at the back of the printer. The connection to the M20 is shown in figure 2-3. The mains cable of the printer has to be connected to a suitable power outlet. AFTER ONE HAS VERIFIED THAT THE VOLTAGE INDICATED ON THE STICKER OF THE PRINTER INDICATES THE SAME VOLTAGE AS THE POWER OUTLET GOING TO BE USED.

Fig. 2-3 Connecting Printer to Basic Module

2-6 4100380 V

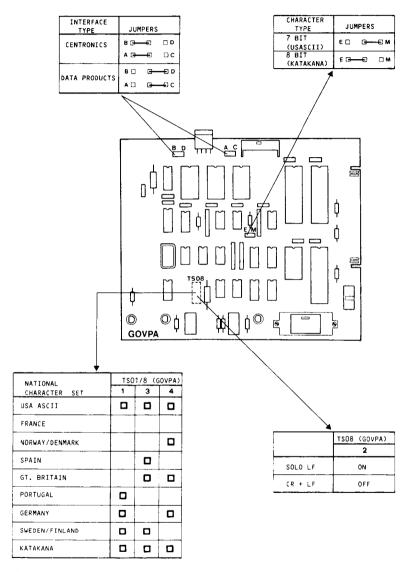

# 2.7.3.1 PR 2400 GOVPA Jumper Settings

☐ = DIPSWITCH ON

# 2.7.3.2 PR 1450 Jumper Settings

### Board BA056

|                              |   |   | TS09 |   |   |   |

|------------------------------|---|---|------|---|---|---|

| OPTIONAL VARIANTS            | 1 | 2 | 3    | 4 | 5 | 6 |

| NOT USED                     | - |   |      |   |   |   |

| AUTO LF ON                   |   |   |      |   |   |   |

| AUTO LF OFF                  |   |   |      |   |   |   |

| MODULO 4"                    |   |   |      | 0 |   |   |

| MODULO 8.5"                  |   |   |      | 0 |   |   |

| MODULO 11"                   |   |   |      |   |   |   |

| MODULO 12"                   |   |   |      |   |   |   |

| 16.6 CHAR/INCH               |   |   |      |   |   |   |

| 10 CHAR/INCH                 |   |   |      |   |   |   |

| PRINT III                    |   |   |      |   |   | 0 |

| IGNORES UNKNOWN<br>CHARACTER |   |   |      |   |   |   |

| NATIONAL       |   | TS08 |   |   |

|----------------|---|------|---|---|

| CHARACTER SET  | 1 | 2    | 3 | 4 |

| SPAIN          |   |      |   |   |

| INTERNATIONAL  | 0 | 0    |   |   |

| GERMANY        |   |      | 0 |   |

| PORTUGAL       |   |      | 0 | 0 |

| DENMARK/NORWAY |   |      |   |   |

| FRANCE         |   |      |   |   |

| ITALY          |   |      |   | 0 |

| SWEDEN/FINLAND |   |      |   |   |

| GT. BRITAIN    |   |      |   |   |

| USA ASCII      |   |      |   |   |

| SWITZERLAND    |   |      | 0 |   |

■ = DIPSWITCH ON

= DIPSWITCH ON

| VARIANTI PRESTAZIONALI                       | F        | NO | 01 |   |

|----------------------------------------------|----------|----|----|---|

| Optional Variants                            | 1        | 2  | 3  | 4 |

| MODULO 4"<br>Module 4"                       | 1        |    | 1  |   |

| MODULO 8.5"<br>Module 8.5"                   | 0        |    | 1  |   |

| MODULO 11"<br>Module 11"                     | 1        |    | 0  |   |

| MODULO 12"<br>Module 12"                     | 0        |    | 0  |   |

| 16.6 CAR/INCH                                |          |    |    | 1 |

| 10 CAR/INCH                                  |          |    |    | 0 |

| STAMPA III - Print III                       |          | 1  |    |   |

| IGNORA CAR.SCONOSCIUTO Ignores unknown char. | <u>i</u> | 0  |    |   |

| SET GRAFICO-VARIANTI NAZIONAL            | .I | P | ON | 02 |   |

|------------------------------------------|----|---|----|----|---|

| Graphic Set-National Variants            |    | 1 | 2  | 3  | 4 |

| INTERNAZIONALE<br>International          |    | 1 | 14 | 1  | 1 |

| GERMANIA<br>Germany                      |    | 1 | 1  | 1  | 0 |

| PORTOGALLO<br>Portugal                   |    | 1 | 1  | 0  | 1 |

| SPAGNA<br>Spain                          |    | 1 | 1  | 0  | 0 |

| DANIMARCA - NORVEGIA<br>Denmark - Norway |    | 1 | 0  | 1  | 1 |

| FRANCIA<br>France                        |    | 1 | 0  | 1  | 0 |

| ITALIA<br>Italy                          |    | 1 | 0  | 0  | 1 |

| SVEZIA - FINLANDIA<br>Sweden - Finland   |    | 1 | 0  | 0  | 0 |

| REGNO UNITO<br>United Kingdom            |    | 0 | 1  | 1  | 0 |

| USA - ASCII<br>USA - ASCII               |    | 0 | 1  | 0  | 1 |

| SVIZZERA<br>Switzerland                  |    | 0 | 1  | 1  | 1 |

| VARIANTI PRESTAZIONALI         | PON<br>1                                         | 03<br>2 |

|--------------------------------|--------------------------------------------------|---------|

| Optional Variants IGNORA CR ON | <del>-                                    </del> | 1       |

| IGNORE CR OFF                  |                                                  | 0       |

| AUTO LF ON                     | 1                                                |         |

| AUTO. LF OFF                   | 0                                                |         |

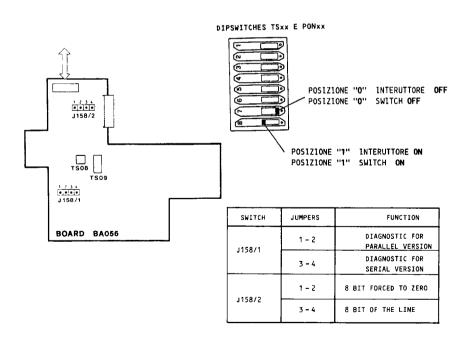

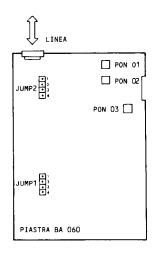

# DIPSWITCHES TSxx E PONxx

| PONTICELLO<br>Jumper | PONTICELLATO IN<br>Jumper Connection | FUNZIONE<br>Function                                                  |

|----------------------|--------------------------------------|-----------------------------------------------------------------------|

| JUMP 1               | 1 - 2                                | DIAGNOSTICA PER VERSIONE PARALLELA<br>Diagnostic for Parallel Version |

| 30117                | 3 - 4                                | DIAGNOSTICA PER VERSIONE SERIALE<br>Diagnostic for Serial Version     |

| JUMP 2               | 1 - 2                                | 8° BIT DA LINEA<br>8th bit from line                                  |

| JUMP 2               | 3 - 4                                | 8° BIT FORZATO A ZERO<br>8th bit forced to zero                       |

POSIZIONE "O"

INTERRUTT. OFF

"O" position

switch OFF

POSIZIONE "1"

INTERRUTT. ON

"1" position

switch ON

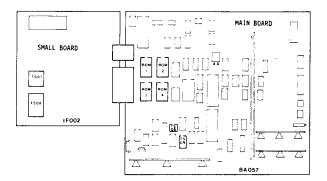

# 2.7.3.3 PR 1471 Jumper Settings

|           |       |       | 1  |            |                                              | 902 |            |

|-----------|-------|-------|----|------------|----------------------------------------------|-----|------------|

|           |       |       | 4  | 7          | _[3]                                         | 3   | 3          |

| INTERFACE | CENTR | ONICS |    |            |                                              |     |            |

| INTERFACE | DATA  |       | Ī  |            |                                              | -   |            |

| RAM D     | ł k   | - "   | Ť  | Ť          |                                              |     | 0          |

| RAP 2     | K     |       | 1  | , (        | _                                            |     |            |

| RAM 4     | к     |       | 1  | 1          |                                              |     |            |

|           |       |       | .1 |            |                                              |     | i          |

|           |       |       | Ţ  | IFO<br>ISO |                                              |     | <u>i -</u> |

|           | ,     | 8175  |    | TS0        | <u>,                                    </u> |     | i          |

| DPTIONAL VARIANTS                      | BA052 - BA057<br>TS09 |   |   |   |  |

|----------------------------------------|-----------------------|---|---|---|--|

|                                        | 1                     | 2 | 3 | 4 |  |

| (H AFTER LF                            | В                     | ĺ |   |   |  |

| SCONO SIGNAL FOR<br>UN KNOWN CHARACTER |                       | 0 |   |   |  |

| LF AFTER CR                            |                       |   | _ |   |  |

| LOCAL SETTING FOR BEL                  | L                     |   |   | 0 |  |

= DIPSHITCH ON

| FORMS TYPE                   |   | BADS2 - BADS7<br>TSDB |   |   |  |  |  |

|------------------------------|---|-----------------------|---|---|--|--|--|

|                              | 1 | 2                     | 3 | 4 |  |  |  |

| DISABLE VERTICAL PROGRAMMING |   |                       |   |   |  |  |  |

| SPECIAL FORMS                |   |                       |   |   |  |  |  |

| SPECIAL FORMS                |   |                       |   | L |  |  |  |

| FORMS 3"                     | 0 | ۵                     |   |   |  |  |  |

| FORMS 4"                     |   |                       | 0 |   |  |  |  |

| FORMS 5"                     | _ |                       | 0 |   |  |  |  |

| FORMS 6"                     |   | ם                     | 0 |   |  |  |  |

| FORMS ?"                     | 0 | 0                     | _ |   |  |  |  |

| FORMS 8"                     |   |                       |   | 0 |  |  |  |

| FORMS 9"                     | 0 |                       |   |   |  |  |  |

| FORMS 10"                    |   | 0                     |   | 0 |  |  |  |

| FORMS 11"                    | 0 | 0                     |   | 0 |  |  |  |

| FORMS 12"                    |   |                       | _ | 0 |  |  |  |

| FORMS 13"                    | 0 |                       | ۵ | ٥ |  |  |  |

| FOR#S 14"                    |   | 0                     | 0 | 0 |  |  |  |

| FORMS 8.5                    | _ | В                     |   | 0 |  |  |  |

| • | z | DIPSWITCH | ON |

|---|---|-----------|----|

| _ |   |           |    |

| NATIONAL CHARACTER SET | TS09 |     |   |   |  |  |

|------------------------|------|-----|---|---|--|--|

|                        | 5    | . 6 | 7 |   |  |  |

| SPAIN                  |      |     | 0 |   |  |  |

| USA ASCII              |      |     |   |   |  |  |

| INTERNATIONAL          | 0    | -   |   |   |  |  |

| GERMANY                | 1    | 0   |   |   |  |  |

| PORTUGAL               | 0    | 0   |   |   |  |  |

| DENMARK/NORWAY         | _    |     | 0 |   |  |  |

| FRANCE                 |      | 0   | 0 |   |  |  |

| ITALY                  | 0    | 0   | 0 |   |  |  |

| SWEDEN/FINLAND         | 1    |     |   | 0 |  |  |

| SWITZERLAND            | 0    |     |   | 0 |  |  |

| GT. BRITAIN            | 1    | 0   |   | 0 |  |  |

| USA ASCII/2            | 0    | 0   | _ | 0 |  |  |

| YUGOSLAVIA             | 1    |     | D | 0 |  |  |

| ICELAND                | 0    |     | _ | 0 |  |  |

| JAPAN                  | T    | 0   | 0 | 0 |  |  |

| RESERVED               | 0    | 0   |   | 0 |  |  |

a DIPSWITCH ON

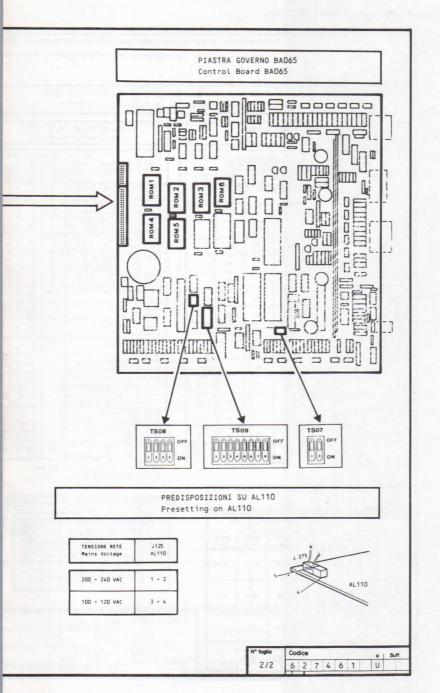

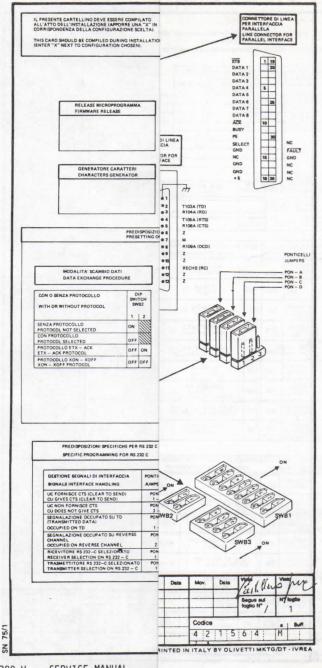

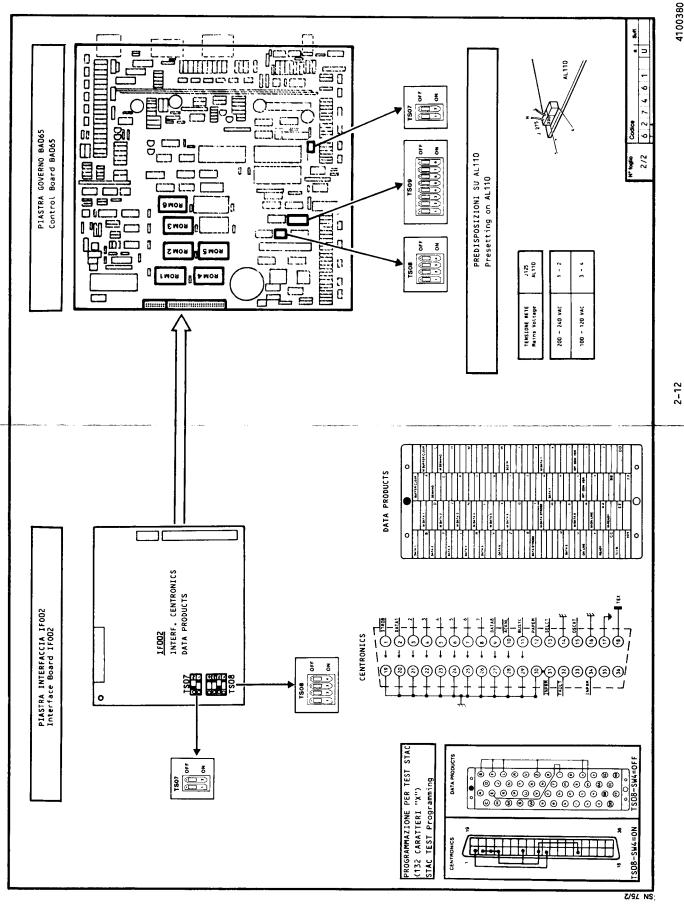

|                                                                             |                    |               |          | SCELTA |                       |            |           |                               |      |

|-----------------------------------------------------------------------------|--------------------|---------------|----------|--------|-----------------------|------------|-----------|-------------------------------|------|

|                                                                             |                    |               |          |        | PIASTR                |            |           | CIA IFO0                      | 02   |

|                                                                             | -                  |               |          | _      |                       |            | _         |                               | -    |

|                                                                             | SET GRAF           |               |          |        |                       |            |           |                               |      |

|                                                                             | or apirite t       |               | Juner    |        |                       |            |           |                               |      |

| NAZI                                                                        |                    |               |          |        |                       | T 1 THE 8  |           |                               |      |

| (CRT 300)<br>ROM A                                                          | (CRT 3)            | 01)<br>B      | NAZ1     | Memor  | y Capac               | ity        | `         |                               |      |

| U.S.A. ASCII                                                                | GRECIA<br>Greece   |               |          |        |                       | SEGNALI SU |           |                               |      |

| INTERNAZIONALE<br>International                                             | RUSSIA             | 1             | QN       |        | 1NM03                 | IMMOS      | 1         | NM01                          |      |

| GERMANIA<br>Germany                                                         | RUSSIA             | 2             |          |        | SV1                   | SMS.       |           | sw3                           |      |

| PORTOGALLO<br>Portugel                                                      | RISERVA<br>Reserve |               | ON       |        | OH                    |            |           |                               |      |

| SPAGNA<br>Spain                                                             | SET GRA<br>Graphic | FICO          |          |        |                       |            |           |                               |      |

| DANIM./NORV.                                                                | RISERVA            | то            | ON       |        |                       |            |           |                               |      |

| Penmark/Norvai<br>FRANCIA                                                   | RESERVA            |               | _        |        |                       |            |           |                               |      |

| France                                                                      | RESERVA            |               | _        | -      | FOR                   | MATO CA    | RATTER    |                               |      |

| Italy                                                                       | Reserve            |               | ON       | L      |                       | racter     |           |                               |      |

| SVEIIA/FINLAN.<br>Sweden/Finland                                            | GRECIA<br>Greece   |               |          | Г      |                       | T          | SEGNALI   | SU TSO7                       |      |

| SVIZZERA<br>Switzerland                                                     | RUSSIA             | 1             | ON       |        | t DI CODICE<br>de bit |            | Signal    | DATAX                         |      |

| GRAN BRETAGNA<br>6. Britain                                                 | RUSSIA             | 2             |          | -      | 7 817                 | -          | SW1<br>ON | SW2                           |      |

| U.S.A. ASCII                                                                | RISERVA<br>Reserve |               | ON       |        | 8 B1T                 |            | OFF       | ON                            |      |

| JUGOSLAVIA<br>Iugoslavia                                                    | SET GRA<br>Graphic | FICO          |          |        |                       |            |           |                               |      |

| ISLANDA                                                                     | RISERVA            | то            | ON       |        |                       |            |           |                               |      |

| Iceland                                                                     | RESERVA            | то            |          |        |                       |            |           |                               |      |

| Japan<br>RISERVATO                                                          | RESERVA            | _             |          |        |                       |            |           |                               |      |

| Reserved                                                                    | Reserve            |               | ON       |        |                       |            |           |                               |      |

|                                                                             |                    |               |          |        |                       |            |           |                               |      |

|                                                                             | VARIANT            |               |          |        |                       |            |           |                               |      |

|                                                                             | Operati            | onat Va       | rian     |        | 115                   | O INTE     | RFACCI    |                               |      |

| VARIANTE                                                                    | Tall               |               | PR       |        |                       | erface     |           |                               |      |

| Verient                                                                     | No.                | CRLFO<br>SW 1 | SC<br>SI |        |                       |            | TS08-     | EW4                           |      |

| FORZA CR DOPO                                                               | THE S              | Ti-           |          |        | CENTRON<br>DATA PR    |            | OFF       | -                             |      |

| MOVIMENTO CARTA<br>Carriage return<br>after line feed                       |                    | ON .          |          |        | DATE OF               |            | 0.7       | _                             |      |

| COMPATTA MESSAGE<br>PER CARATTERE SC<br>Message packing<br>event of uncknow | OMOSCIUTO<br>in    | -             |          |        |                       |            |           |                               |      |

|                                                                             |                    |               |          | Mov.   | Data                  | Mov.       | Deta      | vieto Cay                     | Vist |

| FORZA-LF DOPO CR                                                            |                    | -             | -        | -      | -                     |            |           | Segue sul<br>toglio N°<br>2/2 | Nº 5 |

| FORZA-LF DOPO CR<br>Line feed after<br>carriage return                      |                    |               |          |        |                       |            |           |                               |      |

| Line feed after                                                             | BELL               |               |          |        | -                     | Codice     |           | 2/2                           | 1    |

# 2.7.3.5 PR 2300 Jumper Settings

4100380 V SERVICE MANUAL

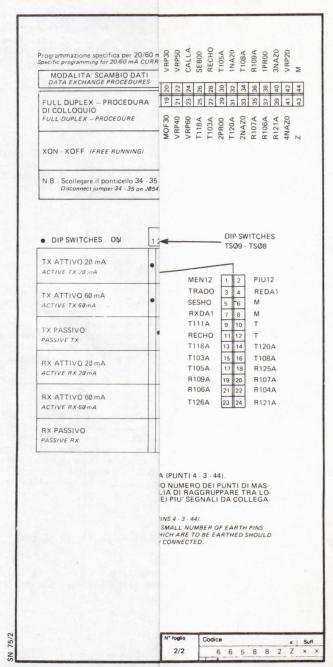

Programmazione generica — General programming

| MODO DI FUNZIONAMENTO OPERATING MODE                               | JØ54<br>(G0Ø92) |

|--------------------------------------------------------------------|-----------------|

| TEST STAC<br>STAC TEST                                             |                 |

| FREE RUNNING                                                       | 4 - 17          |

| FULL-DUPLEX - PROCEDURA<br>DI COLLOQUIO<br>FULL-DUPLEX - PROCEDURE | 4 - 18          |

|                                                                    |                 |

| XON - XOFF (FREE - RUNNING)                                        | 4 - 18 - 19     |

| VARIANTI PRESTAZIONALI<br>OPERATIONAL VARIANTS                                                | J054<br>(G0092) |

|-----------------------------------------------------------------------------------------------|-----------------|

| INVIO BREAK ALL'ACCEN-<br>SIONE (240 msec.)<br>BREAK GENERATION UPON<br>SWITCH-ON (240 msec.) | 4 - 20          |

| TEST CONTINUO (VRP 40)<br>CONTINUOUS TEST (VRP 40)                                            | 4 21            |

| FORZA CR DOPO MOVIMENTO<br>CARTA (VRP 50)<br>CARRIAGE RETURN AFTER<br>LINE FEED (VRP 50)      | 4 - 22          |

| PONI LOCALE PER BELL (VRP 60) LOCAL SETTING FOR BELL (VRP 60)                                 | 4 - 23          |

| FORZA LF DOPO CR (NAZ40)  LINE FEED AFTER CARRIAGE RETURN                                     | 4-41            |

| J054<br>(G0092) |

|-----------------|

| 4 - 8           |

|                 |

|                 |

| 4 - 10          |

| 4 - 9           |

| 4 - 12          |

| 4 - 11          |

|                 |

|                 |

|                 |

|                 |

| VELOCITA' SCAMBIO DATI<br>DATA EXCHANGE SPEED | J054<br>(G0092)  |

|-----------------------------------------------|------------------|

| 110 BpS<br>110 bits per second                |                  |

| 134,5 BpS                                     | 4 - 13 - 15 - 16 |

| 150 BpS                                       | 4 16             |

| 200BpS                                        | 4 - 13 - 15      |

| 300BpS                                        | 4 - 15           |

| 600 BpS                                       | 4 - 13 - 16      |

| 1200 BpS                                      | 4 - 14           |

| 1800 BpS                                      | 4 - 14 - 16      |

| 2400 BpS                                      | 4 - 15 - 16      |

| 4800 BpS                                      | 4 - 14 - 15      |

| 9600 BpS                                      | 4 - 14 - 15 - 16 |

| TENSIONE RETE<br>MAINS VOLTAGE | TRASFORMATORE T362<br>TRANSFORMER T362 |       |                             |  |  |

|--------------------------------|----------------------------------------|-------|-----------------------------|--|--|

|                                | COLLE<br>CONNE<br>FASE1                | FASE2 | PONTICEL-<br>LARE<br>JUMPER |  |  |

| 100V - 60 Hz                   | 1                                      | 3     | 4 - 8.2 - 7                 |  |  |

| 115V - 60 Hz                   | 1                                      | 5     | 6 - 9,2 - 7                 |  |  |

| 220V - 60 Hz                   | 1                                      | 9     | 6 – 7                       |  |  |

| TENCIONE DETE                  |        | FORMA                            | TORE T361<br>MER T361       |

|--------------------------------|--------|----------------------------------|-----------------------------|

| TENSIONE RETE<br>MAINS VOLTAGE | FASE 1 | GARE<br>CTION<br>FASE2<br>PHASE2 | PONTICEL-<br>LARE<br>JUMPER |

| 100V - 50 Hz                   | 1      | 3                                | 4 - 8,2 - 7                 |

| 120V - 50 Hz                   | 1:     | 5                                | 6 - 9,2 - 7                 |

| 200V - 50 Hz                   | .1     | 8                                | 4 - 7                       |

| 220V - 50 Hz                   | 1      | 8                                | 6 – 7                       |

| 240V - 50 Hz                   | 1      | 9                                | 6 – 7                       |

| oliv       | vetti            | - |

|------------|------------------|---|

| Prodotto ) | KU7750           | - |

| Firma      | Data<br>18-12-80 |   |

| Descrizione | PR430 | (CON ALI 254) |

|-------------|-------|---------------|

|             |       |               |

PIASTRE : AT633 - GOØ92 - IFØ63

CARTELLINO DI SPECIALIZZAZIONE Specialization Card

| Mov. | Data    | Mov.   | Da | ta | Visto | ux   | 1  | Vist | 0     |    |

|------|---------|--------|----|----|-------|------|----|------|-------|----|

| AGG. | 19-3-82 |        |    |    |       | o N° | ıt | Nº I | oglio |    |

|      |         | Codice |    |    |       |      |    | α    | Su    | H. |

|      | -       | 6      | 6  | 5  | 8     | 8    | 2  | Z    | ×     | ×  |

### 2.7.4 CONNECTING TO AN AC SOURCE

The power switch on the Basic Module as well as the power switch on the printer should be off. The AC mains cable exits from the rear of the Basic Module. This cable should be connected to an appropriate power outlet, AFTER HAVING VERIFIED THAT THE VOLTAGE INDICATED ON THE STICKER AT THE REAR OF THE BASIC MODULE INDICATES THE SAME VOLTAGE AS THE POWER OUTLET TO BE USED. Two wire extensions should not be used.

# 2.7.5 SWITCHING ON (CPU 1042)

Insert the system diskette in one of the disk drives. The power switch on the Basic Module can now be switched on. The Light Emitting Diode (LED) on the keyboard should light up. If the LED does not light one has to immediately check the power outlet. If the LED is on, after about  $8\,$ seconds the following should appear on the display:

M20 system configuration:

total memory size: XXX kbytes

user memory size: XXX kbytes

display tpe: XXX kbytes

Black and White or Color display tpe: disk drive(s):

X ready

L1.M20 PCOS VER. XX

This means that the Power Up diagnostics have run successfully. Power up diagnostics which are run automatically after switching on or after pushing the RESET button verify that enough of the M20 functions are operable to allow the running of additional diagnostic programs. If the power up diagnostics do not run to completion an error code should appear on the Display and on the printer. Refer to the power Up diagnostics chapter for a detailed account of these diagnostics.

Turning the printer on and off while the computer is in use may cause abnormal operation and the computer may 'hang up', requiring the user to reset the system. It should be pointed out to the customer that he should not switch on and off the system unnecessarily. Should something go wrong during the operation of the system, the user should first press the Control key in conjunction with the RESET key on the keyboard. If this operation has no effect the RESET button located at the right rear side of the Basic Module should be pressed.

# 2.7.5.1 Procedures To Be Followed When Installing Hard Disk Systems

This section describes the procedure for installing PCOS on a hard disk M20 system. This section covers both the first installation and also updating the hard disk drive with a new version of PCOS.

2-16

The first thing to do is format the hard disk drive. To format the hard disk drive you must first load PCOS from the diskette you received with the system. Do this by inserting the PCOS system diskette in the floppy disk drive and turning on power to the system. Press the "f" key on the keyboard before the two beeps are heard. This causes the Bootstrap ROM to load PCOS from the floppy disk rather than from the hard disk. This is necessary because there may be older versions of PCOS or test programs remaining on the hard disk drive from the Manufacturing Test process.

After PCOS is loaded type "vf 10:". This tells PCOS to run the Vformat program and to format the hard disk drive (drive 10). Vformat will tell you each cylinder on the hard disk that is being formatted.

When the Vformat program is complete (as signified by the message Formatting Complete), the next step is to put a bootstrap file on the hard disk. Do this by typing "ps 10:". This invokes the Psave utility to install the current version of PCOS on the hard disk drive. When the Psave utility is complete it wll automatically re-boot the PCOS on the hard disk.

The next step is to copy all the PCOS commands to the hard disk drive. This is done by using the PCOS Fcopy command. To copy all the floppy disk files to the hard disk type "fc 0:\* 10:". The Fcopy will copy all of the files from the floppy diskette to he hard disk. Below is a flowchart illustrating this procedure.

| !    | Insert PCOS disk in mini-floppy                                             | -<br>/!<br>! |                                                 |

|------|-----------------------------------------------------------------------------|--------------|-------------------------------------------------|

|      |                                                                             | •            |                                                 |

| !    | Switch on M2O System                                                        | !            |                                                 |

|      |                                                                             |              |                                                 |

| !!!  | Press "f" key on the keyboard<br>before the two beeps are<br>heard          | !!!          |                                                 |

|      | !<br>!<br>!                                                                 |              |                                                 |

| !    | Type in vf 10:                                                              | !            |                                                 |

|      | !<br>!<br>!                                                                 | -            |                                                 |

| !!!! | Message: Formatting Complete<br>appears if formatting was<br>was successful | !!!          |                                                 |

|      | !<br>!                                                                      |              |                                                 |

| !    | Type in ps 10:                                                              | !            |                                                 |

|      | !<br>!<br>!                                                                 | -            |                                                 |

| !    | Type in fc 0:* 10:                                                          | !            |                                                 |

|      | !                                                                           |              | -Question "Do you want<br>to overwrite PCOS.SAV |

| !    | INSTALLATION COMPLETE                                                       | !            | (y,n)?"<br>Type "n".                            |

#### UPDATE INSTALLATION

If the hard disk drive has been through the initial installation (as described above), and all that is required is to place the latest version of PCOS and the utilities on the hard disk, the following procedure should be used. Boot the hard disk system and then place the new PCOS diskette in the floppy disk drive. Type "fc %f 0:\* 10:" which will invoke the Fcopy utility to copy all the files from the floppy diskette to the hard disk. The "%f" (force) option will cause Fcopy to copy the files to the hard disk even though the files may already exist on the hard disk.

NOTE: THIS PROCEDURE DOES NOT CALL FOR FORMATTING THE HARD DISK AND THEREFORE WILL NOT HARM OTHER FILES THAT MAY BE PRESENT ON THE HARD DISK.

# 2.8 UPGRADES

This section deals with the upgrades made in the field on the M20 system. The first upgrades or installations described include:

- memory upgrade

- IEEE 488 Interface Board installation

- Second mini-floppy disk drive installation

- Twin RS 232C Interface Board installation

- APB 1086 Board installation

- Colour Display Installation

### 2.8.1 MEMORY UPGRADE

Materials required:

Memory Expansion Board

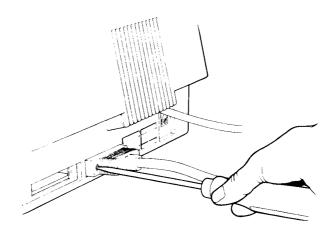

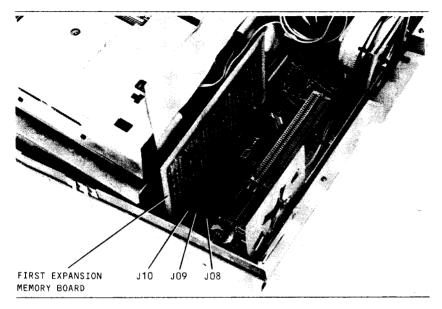

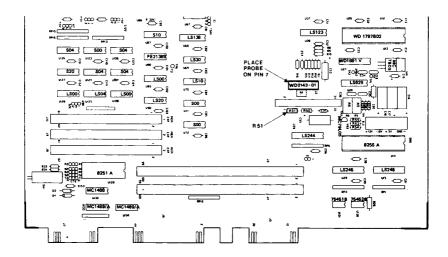

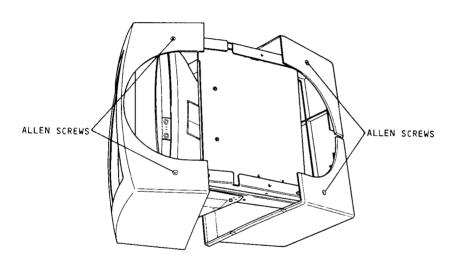

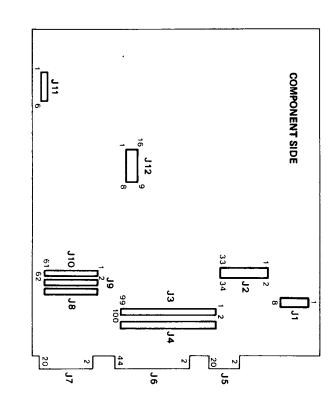

The memory board to be installed (whether 32KB or 128KB type) plugs into slot J10 on the motherboard, that is the slot nearest the front of the Basic Module. The first thing to do is remove the Basic Module cover. This is done by untightening the two screws at the rear of the Basic Module and then lifting the rear of the cover. Ensure jumper X2-7 on the motherboard is open. See jumper chart tables at end of this section.

In order to install the memory board, plug it into slot J10 with the com-

ponent side facing the front of the machine.

Fig. 2-4 Installation of memory expansion board

One can also install a second or third plug in memory board. The procedure is the same except that the second plug in board plugs into connector J9 and the third plug in board plugs into connector J8. Finally, reinstall the Basic Module cover.

NOTE: ONE CAN ONLY INSTALL MEMORY BOARDS OF THE SAME TYPE i.e. one cannot mix 32KB type boards and 128KB type boards.

2-20 4100380 V

| CONFIGURATION                                             | Z1-Z-Z2 | K1-K-K2 | E1-E-E2 | v1-v-v2 | W1-W-W2 | M1-M-M2 | x1 - x8 | X2 - X7 | x3 - x6 | U62/3/4/5          | U86 i |

|-----------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|--------------------|-------|

| M 20 WITH OUT<br>ANY EXPANSION<br>BOARDS                  | z - z1  | K - K2  | E - E1  | v - 41  | w - w2  | н - м1  | OFF     | ON      | OFF     | ICs PRESENT        | OFF   |

| M 20 WITH AT<br>LEAST ONE B/W<br>32KB EXPANSION<br>BOARD  | 2 - 21  | K - K 2 | E - E1  | v - v1  | M - MS  | M - H1  | OFF     | OFF     | OFF     | ICS PRESENT        | OFF   |

| M 20 WITH AT<br>LEAST ONE B/W<br>128KB EXPANSION<br>BOARD | z - z1  | K - K1  | E - E1  | v - v2  | u - u1  | M - M2  | ON      | OFF     | OFF     | ICS NOT<br>PRESENT | on    |

| M 20 WITH ONE<br>32KB COLOUR<br>BOARD<br>(4 COLOURS)      | z - z1  | K - K2  | E - E1  | v - v1  | M - MS  | м - и1  | OFF     | OFF     | ON      | ICs PRESENT        | OFF   |

| M 20 WITH ONE<br>128KB COLOUR<br>BOARD<br>(4 COLOURS)     | 2 - 21  | K - K1  | E - E1  | v - v2  | u - w1  | M - M2  | OFF     | ON      | ON      | ICS NOT<br>PRESENT | ON    |

| M 20 WITH TWO<br>32KB COLOUR<br>BOARDS<br>(8 COLOURS)     | z - z1  | K - K2  | E - E2  | V - V1  | W - W2  | m - m1  | ON      | OFF     | ON      | ICs PRESENT        | OFF   |

| M 20 WITH TWO<br>128KB COLOUR<br>BOARDS<br>(8 COLOURS)    | z - z1  | K - K1  | £ - E2  | v - v2  | w - w1  | M - M2  | ON      | ON      | ON      | ICS NOT            | 01    |

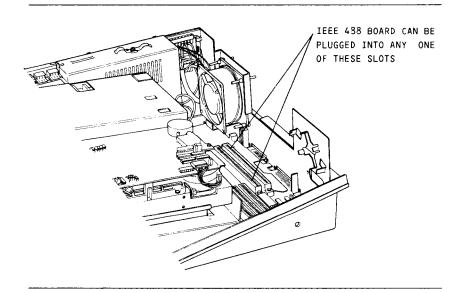

### 2.8.2 IEEE 488 INTERFACE

Materials required: IEEE 488 Interface Board Signal ribbon cable which connects board to rear of Basic Module IEEE Peripheral Cable

The IEEE 488 interface board plugs into slot J3 or J4 on the motherboard. The first thing to do is to remove the Basic Module cover. This is done by first untightening the two screws at the back of the Basic Module cover and then lifting the rear of the cover.

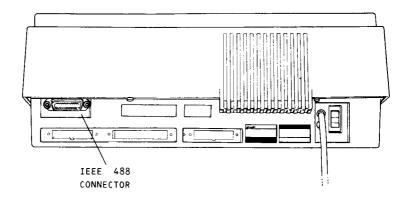

In order to install the IEEE 488 interface board, plug it into slot J3 or J4 on the motherboard with the component side facing the front of the machine. A flat ribbon cable plugs into the connector J1 on the IEEE board. The other end of the flat cable has a connector which has to be screwed to the back of the Basic Module cover. Peripherals are connected to the M20 by means of a cable (PIC1037) which plugs into the connector at the back of the Basic Module cover.

Fig. 2-5 Installation of IEEE board

Fig. 2-6 IEEE 488 connector at rear of Basic Module

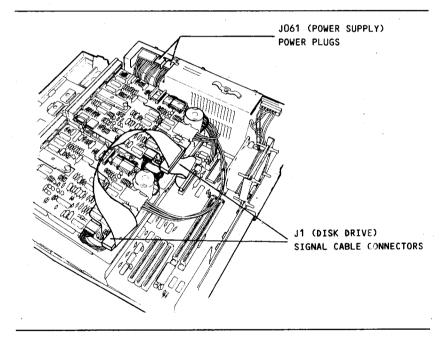

# 2.8.3 INSTALLATION OF SECOND MINI-FLOPPY DISK DRIVE

Materials Required: Mini-Floppy Disk Drive Signal Ribbon Cable (with three connectors) Power Cable Terminator Resistor (preferably 330 ohm)

NOTE: The right hand disk drive in this manual is drive 0, while the left hand one is drive 1. In other manuals (Mini-Floppy General Service Manual) the numbering may be different.

The following steps should be followed when installing a second disk drive:

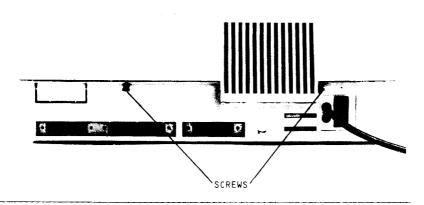

- 1) Remove the Basic Module cover by looening the two screws at the rear of the Basic Module and then lifting the rear of the cover.

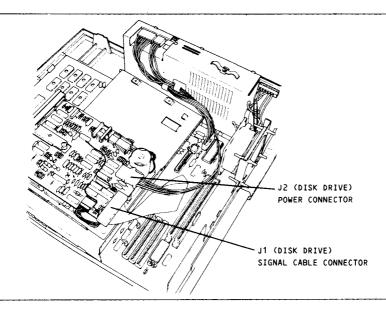

- 2) Remove the ribbon connector from J2 on the motherboard and from J1  $\,$  on the disk drive PCB.

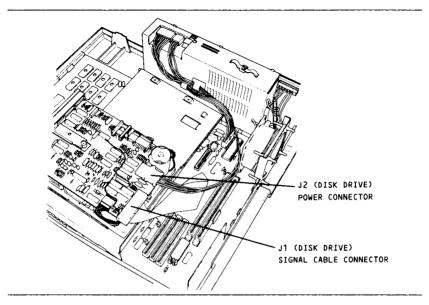

- 3) Remove the power connector from the disk drive connector J2. J2 is the disk drive DC power connector and is located near the spindle drive motor and mounted on the component side of the disk drive PCB.

Fig. 2-7 M20 with one Mini-Floppy Disk drive

- 4) Remove the whole metal base of the mini-floppy disk drive by first sliding the base slightly forward and then lifting the base from the Basic Module.

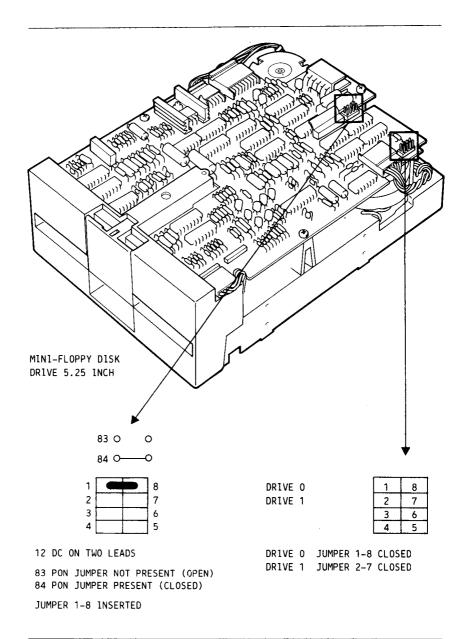

- 5) Remove the metal cover of the original disk drive by loosening the two screws on each side. This original disk drive is identified as disk drive number 0. Ensure that this disk drive is jumpered for disk drive number 0. Refer to the Mini-Floppy General Service Manual for further details. THE TERMINATOR RESISTORS MUST BE PRESENT IN ALL THE UNITS OF THE DAISY CHAIN.

Replace the metal cover.

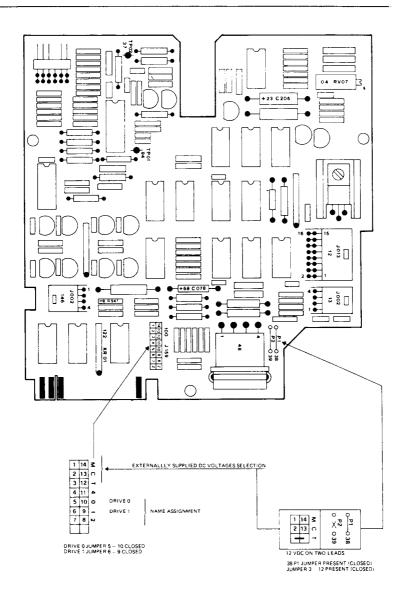

- 6) Remove the metal cover of the disk drive to be installed by loosening the two screws on each side. Ensure that this disk drive is jumpered for drive number 1 and the supply voltage jumpers are correctly fitted. The M20 provides the mini-floppy disk drive with +12VDC ON TWO LEADS. Refer to the General Service Manual of the Mini-Floppy Disk Drive. THE TERMI-NATOR RESISTORS MUST BE PRESENT IN ALL THE UNITS OF THE DAISY CHAIN. N.B. THERE ARE TWO TYPES OF TERMINATOR RESISTORS 150 OHM ONES AND 330 OHM ONES. IF 150 OHM ONES ARE USED. PLEASE REFER TO THE FOLLOWING TABLE:

### BOARD ATO64

DRIVE 0: 150 ohm terminator (only pins 1 and 4 inserted)

DRIVE 1: 150 ohm terminator inserted

BOARD AT109

DRIVE 0: 150 ohm terminator (only pins 1 and 5 inserted)

DRIVE 1: 150 ohm terminator inserted

Pin 1 is marked with a small dot.

- 7) Place the new disk firmly on the metal base. Tighten the screw at the front.

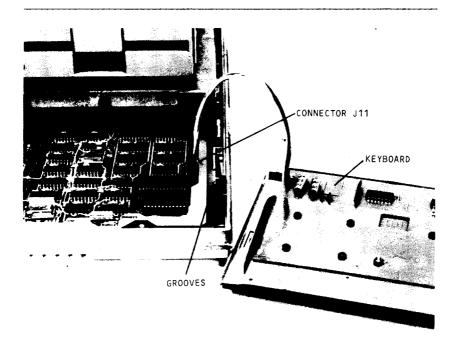

- 8) Place the whole metal base with the two mini-floppy disk drives mounted on it back again in the Basic Module. There are 6 grooves on the bottom of the Basic Module in order to ensure that the whole metal base is properly seated.

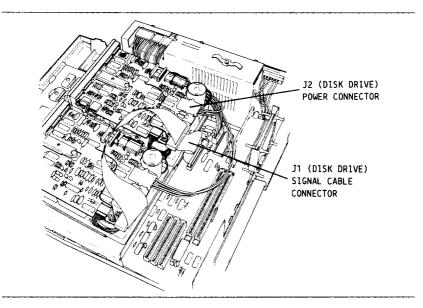

Fig. 2-8 M20 with two Mini-Floppy Disk Drives

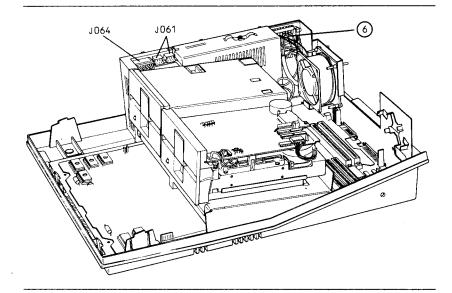

- 9) Connect the power cable to drive 0. This power cable from connector J061 on the power supply in the Basic Module plugs into the DC power connector J2 on disk drive 0. J2 is located near the spindle drive motor and is mounted on the component side of the PCB on the disk drive.

- 10) Connect power cable to disk drive 1. This power cable from connector J061 on the power supply in the Basic Module plugs into the DC power connector J2 on disk drive number 1. J2 is located near the spindle drive motor and is mounted on the component side of the PCB on disk drive number 1. Note that the two connectors on the power supply nearest the potentiometer

are both J061 and both provide identical DC voltages to the disk drives.

- 11) Connect the signal cable to the disk drives. The signal cable has three connectors: the first one fits into connector J2 on the mother-board, the second one fits into connector J1 on the disk drive 0, the third one fits into connector J1 of disk drive 1. Ensure that the cable connector that fits into the disk drive number 1 is oriented so that the cable exits from the bottom.

- 12) Install the new front cover of the disk drives.

- 13) Replace the Basic Module cover.

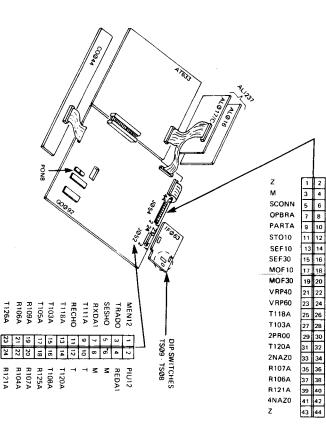

Fig. 2-9 Setting of electronic board AT064

4100380 V SERVICE MANUAL

Fig. 2-10 Setting of electronic board AT109

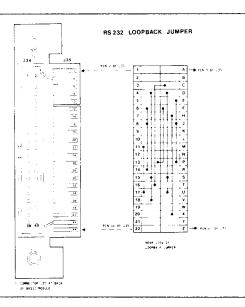

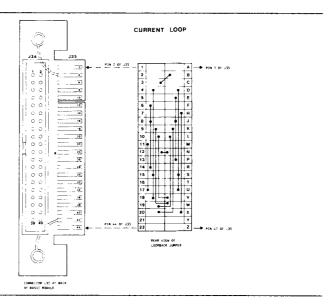

### 2.8.4 TWIN RS 232C INTERFACE BOARD

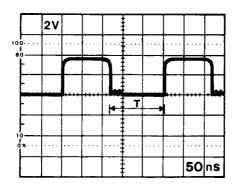

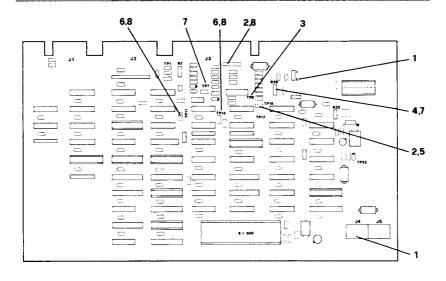

Materials Required: Twin RS 232C Board Flat ribbon cable Card Edge Connector Cable to connect peripheral (s)